Синхронный детектор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (11) 621083

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) ДОполнительное к авт. свил-ву № 641282

2 (51) М. Кл.

Н 03 К 9/04 (22) 3asa e o 28.03.77(21)2467193/18 21 с присоединением заявки № (23) Приоритет

Ьсударвтвенный неинтет

Сюмтв Иннктроа СИР в дюлак нзейратвннй н етнрытнй (43)-Опубликовано 2g.08 78рюллетеиь № 31 (53) УДК 62 1. 31 7, . 77 (088. 8) (4б) Дата опубликования описания 14.07.78 (72) Автор изобретения

О. Л. Николайчук

Специальное конструкторское бюро. микроалектроникп в приборостроении (71) Заявитель

{54) СИНХРОННЫЙ ДЕТЕКТОР

Изобретение относится к радио- и електроизмерительной технике и может быть использовано в фаэочувствительных, амплитудных вольтметрах, в устройствах выделения синфазной и квадратурной составляющих напряжения и др.

По основному.авт. св. ¹ 541282 известный сьлхронных детектор, содержащий последовательно соединенные первый ключ, операционный усилитель и второй ключ, а также запоминающие конденсаторы, подключенные к выкодам ключей, формирователь, вход которого соединен с источником опорного сигнала, и триггер, вход которого соединен с выходом формирователя, а выходы подключены соответственно к управляющим входам ключей.

Однако известное устройство характеризуется низким быстродействием.

Оель изобретения — повышение быстродействия.

Для достижения поставленной цели в синхронный детектор, содержащий последовательно соединенные первый аналоговый ключ, операционный усилитель и второй аналоговый ключ, запоминающие конденсаторы, подключенные к выходам ключей, и формирователь, вход которого соединен с источником опорного сигнала, и

3 счетный триггер, вход которого соединен с выходом формирователя, а выходы подключены соответственно к управляющим входам ключей, введены второй операционный усилитель, )сумматор,; третий и чет16 вертый аналоговые ключи, причем вход второго операционного усилителя через запоминающий кондесатор соединен с землей, а через третий аналоговый ключ— с входом детектора, выход операционно1з го усилителя через четвертый аналоговый ключ соединен с одним иэ входов сумматора, другой вход которого соединен с выходом второго аналогового клк ча, а управляющие входы третьего и чет2В вертого аналоговых ключей соединены соответственно с инверсным и прямым выходами счетного триггера.

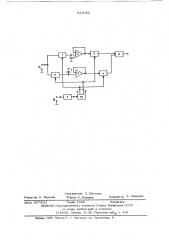

Схема устройства представлена на

25 чертеже.

621083

Предлагаемый синхронный детектор содержит аналоговые ключи 1-4; формирователь 5; запоминающие конденсаторы 6 и 7; операционные усилители 8 ь

9; счетный триггер 10; аналоговый сумматор 11.

Синхронный детектор работает следующим образом. Формирователь 5 из опорного напряжения 0 g формирует. прямоугольные импульсы, которые поступают на счетный вход триггера 10. На прямом Q и инверсном б выходах триггера формируются импульсы с длительностью, равной периоду опорного сигнала U .

Управление аналоговыми ключами 14 осуществляется с выходов 9 и триггера так, что когда открыты ключи

1 и 4, ключи 2 и 3 закрыты.

Korea ключ 1 открыт, напряжение на конденсаторе 6 повторяет входное напряжение U, при этом ключ 3 закрыт и напряжение на. первом входе сумматс ра 11 равно нулю.

В это время ключ 4 открыт и на второй вход сумматора поступает напряжение с конденсатора 7, соответствующее амплитуде входного напряжения ц и фэовому сдвигу между опорным и входным напряжениями, которое запоминается в момент размыкания ключа 2.

В следующий период опорного напряжения закрывается ключ 1, на конденсаторе 6 запоминается напряжение и через открытый ключ 3 поступает на первый вход сумматора, В это время на втором входе на35 пряжение равно нулю, так как закрыт ключ 4, а входное напряжение через открытый ключ 2 поступает на конденсатор

7. В результате на выходе сумматора в любой момент времени напряжение соответствует амплитуде и фазовому сдвигу измеряемого напряжения U относительно опорного Оя . При изменении амплитуды или фазы напряжения О напряже\ ние на выходе сумматора изменяется уже в следующем периоде опорного напряжения, в отличие от известного решения, в котором напряжение на выходе детектора изменялось только во втором периоде опорного напряжения, При этом погрешность детектирования не изменяет Я.

Таким образом, предлагаемое изобретение позволяет повысить быстродействие синхронного детектора в 2 раза, что позволит повысить точность детектирования амплитудно-модулированных сигналов.

Формула изобретения

Синхронный детектор по авт. св.

И.541282, отличающийся тем, что, c целью повышения быстродействия, в него введены второй операционный усилитель, сумматор, третий и четвертый аналоговые ключи, причем вход второго операционного усилителя через запоминающий конденсатор соединен с землей, а через третий аналоговый ключ — с входом детектора, выход операционного усилителя через четвертый аналого« вый ключ соединен с одним из входов сумматора, другой вход которого соединен с выходом второго аналогового ключа, а управляющие входы третьего и че1 вертого аналоговых ключей соединены соответственно с инверсным и прямым вы. ходами счетного триггера.

621083

Составитель 3. 1Бишкова

Редактор Н. Хлудова Тех ред О. П оп ович Корректор A Гриценко

Заказ 4674/51 Тираж 1086 Под ионое

UHHHHH Госупарственного комитета Совета Министров СССР но делам изобретений и открытий

113035, Москва, >i 35, Раушская на6, и. 4/5

Филиал ППП Пате п", г. Ужгороп, ул. Проектная, 4