Амплитудно-временной преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ(621089

ИЗОБРЕТЕНИЯ

Союз Соввтских

Социалистичвских

Рвсяублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополнительное к авт, свил-ву— (22) Заявлено 15.06.73 (21) 1936481/18-21 с присоелинением заявки №вЂ” (23) ПриоритетЯ (5! } М. Кл

Н 03 К 13/20

Гасударственный комнтет

Совета }йнннстроа СССР оо делам нзооретаннй и открытнй (43) Опубликовано 25.08.78.Бюллетень № 31 (53) УДК 681.325 (088.8) (46) Дата опубликования описания 30.06.78

В, Г. Иоффе, A. П. Лиходедов и Ю. B. Пшеничников (72) Авторы изобретения

Куйбышевский ордена Трудового Крвснсго Знамени авиационный институт имени акад. С. П. Королева (71) Заявитель (54) АМПЛИТУДНОВРЕМЕННОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение может быть использовано в радио- и электроизмерительной технике для преобразования амплитуды одиночных или редкоповторяющихся импульсов во временной интервал.

Известен амплитудно-временной преобразователь (АВП), содержащий накопитель подключенный к выходу зарядного устройства, дискриминатор и разрядное устройство } 1) . о

В таком АВП дискриминатор срабатывает в момент, когда ток зарядного уст» ройства равен нулю. Однако его недостатком является наличие погрешности, зависящей от скорости спада входного импуль о са.

Ближайшим по технической сущности к предлагаемому изобретению является

АВП, содержащий зарядное устройство, к выходу которого подключены накопительный конденсатор, переключаемый стабилизатор разрядного тока и вход дискриминатора $2) .

Однако этот АВП имеет пониженную точность преобразования. 25

11елью изобретения является повышение точности преобразования амплитуды импульсов, форма которых отлична от прямоугольной.

Это достигается тем, что в известном

АВП, содержащем зарядное устройство, к выходу которого подключены накопительный конденсатор, переключаемый стабилизатор разрядного тока и вход дискриминатора, к выходу дискриминатора подключены вход устройства временной задержки и первый вход логического элемента совпадения, а выход устройства временной задержки подключен к упрввляюшему входу логического элемента совпадения.

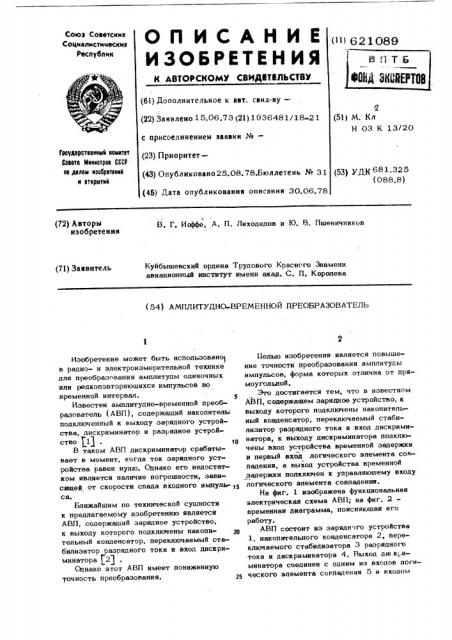

На фиг. 1 изображена функциональная электрическая схема АВП; на фиг. 2временная диаграмма, поясняющая его работу.

АВП состоит иэ заряди го устройства

1, накопительного конденсатора 2, переключаемого стабилизатора 3 разрядного тока и дискриминатора 4. Выход дис к;,иминатора соединен с одним из входов логического элемента совпадения 5 и входом

62 1089

3 устройства 6 временной задержки, выход которого подключен к управляющему входу переключаемого стабилизатора 3 раз.рядного тока и к второму входу логического элемента совпадения 5, <

B исходном состоянии напряжение иа конденсаторе 2 равно нулю. С приходом преобразуемого импульса конденсатор. заряжается до амплитудного значения, а. с затем разряжается малым разрядным то ком стабилизатора 3, В момент, когда входное напряжение станет меньше напряжения на накопительном конденсаторе

2, ток зарядного устройства 1 равен нулю и срабатывает дискриминатор 4.

Устройство 6 временной задержки формирует импульс, задержанный на время ч, для управлении стабилизатороц! 3 разрядного тока. Так как Ф выбирается малым, нвпояжение на конденсаторе эв время задержки практически не изменяется. Фронтом

20 задержанноМ импульса переключается стабилизатор разрядного тока, разрядный ток возрастает и начинается быстрый разряд кондейсатора. Когда напряжение на конденсаторе вновь станет равным нулю

25 дискриминатор 4 сформирует спад выход. ного импульса. Оыходные импульсы дискриминатора и устройстве 6 временной задержки поступают нв входы логическогр элемента совпадении 5, Длительность им 30 пульса на выходе логического элемента совпадения пропорциональна амплитуде . преобразуемого импульса.

Благодаря отличительным признакам изобретения отсутствует погрешность, связанная с неопределенностью фиксации момента прохождения входного сигнала через максимум и зависящая от скорости спада входного сигнала, т.е. повышается точность преобразования амплитуды импульсов, форма которых ощичнв от npgмоугольной.

ФорМула изобретениф

А мплитудно-временноф преобразователь, содержащий зарядное устройство, к выхо ду которого подключены накопительный конденсатор, переключаемый стабилизатор разрядного тока и вход дискриминатора, отличающийся тем,что,с целью повышения точности преобразовании, к выходу дискриминатора подключены вход устройства временной задержки и первый вход логического элемента cosna- дения, а выход устройства временной задержки подключен к управляющему входу переключаемого стабилизатора разрядного тока и к второму входу. логического элемента совладения.

Источники информации, принятые во внимание при экспертизе:

1. Современная ядерная электроника, т. 1, М., Атомиздат, 1974, с. 181182.

2,0,быхчйв.AI)C Жтйыоаьч1ч

due to 1Ие Ооее си .екав. МцсйаЬ

4nskvumenke arrd аеМодь".М Э9

ИЬь, с лЯЬ -2чь.