Устройство цифрового задания трехфазного напряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЮТВЛЬСТВУ

Союз Советских

Соцналмстмческих

Республик ())) 621090 (61) Дополнительное к авт. свид-ву(22) Заявлено 09.03.76 (21) 2337236/18-21 с присоединением заявки №вЂ” (23) Приоритет— (43) Опублнковано25.08 78.Бюллетень № 31 (46) Дата опубликования описания 30.06.78

2 (51) М. Кл

Н 03 К 13/20

Гасударственный комитет

Сееета Иинистрее СССР ее делам нзвбретвни» и еткрмтий (5З) УДК 681 325.(088.8) (72) Авторы изобретения

В. И. Кочерин и Н. С. Баранов (71) Заявитель (54) УСТРОЙСТВО ЦИФРОВОГО ЗАДАНИЯ

ТРЕХФАЗНОГО НАПРЯЖЕНИЯ

Изобретение относится к технике преобразования цифровой величины в аналоговую, а именно в трехфазное напряжение с формой, близкой к синусоидальному закону широтно-импульсной модуляции, и пред- назначается для использования в следяшерегулируемых электроприводах, которые управляются от цифровых вычислительных устройств.

Известны преобразователи цифрового 1о сигнала в трехфазное напряжение с формой, близкой к синусэидальному закону широтно-импульсной модуляции (ШИМ), i которых выходные шины делителя частоты соединены с входом триггерной коль- iS цевой схемы, выходы которой управляют ключевыми элементами трех блоков получения синусоидальных сигналов фаз )1) .;

Выходы блоков синусоидальных сигна- лов соединены с первыми входными шина- 20 ми трех компараторов, вторые входы которых соединены с выходной шиной генератора пилообразного напряжения, управ« ляемого с промежуточной шины делителя ч,астоты. 25

Основным недостатком данного уст ройства является наличие весовых сопротивлений .во всех звеньях, что не позволяет получить малое потребление энергии и выполнить схему в интегральном ис полнении.

Наиболее близким к предлагаемому является устройство, в котором выходные шины кольцевого триггериого делителя через весовые сопротивления соединены с входами трех линейных усилителей и через диоды с прямым и инверсным выходами усилителя, управляюшего амплитудой эталонных аинусоидальных сигналов, выходные шины линейных усилителей поступают на входные шины трех схем сравнения, вторые входы которых соединены с выходной шиной генератора пилообразного напряжения (2j

Здесь так же используется большое количество весовых сопротивлений, что определяет сложность их интегрального исполнения, и сравнние синусоидальных сигналов с пилообразным напряжением

62109 выполняется на схемах, которые имеют изменяющиеся от условий внешней среды уровни срабатывания.

Однако дискретный способ преобразованиУ-и известном устройстве используется в сочетании с аналоговым, что не обеспечивает высокой помехозащищенности и надежности, Бель изобретения — повышение точности, помехозащищенности и надежности.

Это достигается тем, что в устрой30 ство цифрового задания .трехфазного на-, пряжения, содержащее счетчик импульсов, вход которого соединен с шиной стабильной частоты, реверсивный счетчик импульсов, вход которого соединен с шиной

15 задания частоты выходного напряжения, блок умножения, первый вход которого соединен с входными шинами цифрового задания величины выходного напряжения, и и логический блок введены три блока

20 сравнения, выходы которых соединены с первым, вторым и третьим входами логмческого блока соответственно, первые входы первого и второго блоков сравнения соединены с прямым и обратным выко25 дами блока умножения, а первый вход третьего -блока сравнения соединен с ши- ной цифрового задания величины выходного напряжения, а вторые входы всех блоков сравнения соединены с выходом счетчика импульсов, причем выходы младших разрядов реверсивного счетчика (сое- . динены со вторым входом блока умноже ния, а выходы старшего трехфазного разряда этого счетчика соединены с четвер 33 тым, пятым и шестым входами логическЬго блока, выходы которого соединены с шинами выходного сигнала.

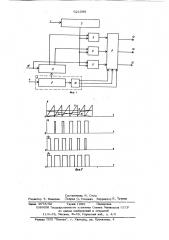

На фиг. 1 приведена структурная электрическая схема предлагаемопо устройся ва; на фиг. 2 - временная диаграмма его работы.

Шина 1 стабильной частоты соединена входом счетчика импульсов 2, выход которого соединен со вторыми входами 4 трех блоков сравнения 3, 4 и 5. Выходы последних; соединены с первым, вторым третьим входами логического блока 6.

Шина 7 задания частоты выходного напряжения соединена с входом реверсивного счетчика 8, в котором вьщелены последовательно соединенные младшие 9 и старший 10 разряды. Бифровые выходы младших разрядов 9 поступают на второй вход блока умножения 1 1, первый вход = которого соединен с шиной 12 цифрового задания величины выходного напряжения.

Шина 12 соединена также с первым входом блока сравнения 5. Прямой выход

0 4. блока умножения 11 соединен с первым входом блока сравнения 3; а обратный выход - с первым входом блока сравнения 4. Выходы старших разрядов 10 соединены с четвертым, пятым и шестым входами логического блока 6, Bblxollbl 13, 14 и 15 которого являются шинами выходного сигнала..Счетчик 2, младшие разряды 9 счетчика 8 и блок умножения

11 выполняются в десятичном коде, Пусть младшие разряды 9 счетчика 8 и блок умножения содержат; по две декады. Старший разряд 10 реверсивного счетчика 8 выполняется с основанием И =6.

Устройство работает следующим образом.

Счетчик импульсов 2 непрерывно суммирует импульсы стабильной частоты

f. СОМGt, При этом на выходах счет чика 2 появляются линейно нарастающие цифровые сигналы, которые при заполнении счетчика сбрасываются в исходное нулевое состояние. Этот процесс проис. ходит непрерывно.

Импульсы задания частоты выходного напряжения поступают на вход реверсивного счетчика 8. При суммировании этих импульсов на выходах младших разрядов

9 появляются линейно нарастающие цифровые сигналы. При заполнении счетчика младших разрядов 9 и сбросе в исходное состояние на выходных .«аршинах старших разрядов 10 появляется очередная цифра от «О» до "5 . В блоке 11 осу ществляется умножение цифровых сигналов с выходов младших разрядов 9 на цифровые сигналы шин 12. При этом на прямых выхцдах блока 11 появляются линейно нарастающие цифровые сит налы, а на обратных - линейно спадак>щие. В исходном (нулевом) положении младших разрядов 9 счетчика 8 на прямых выходах блока 11 выходной сигнал равен нулю, а на обратных имеет максимальное значение. При полном заполнении младших разрядов 9 счетчика 8 значение сигналов на прямых и обратных выходах блока 11 изменяется на противоположное исходному состоянию счет чика. Результат умножения сигналов, соответствующих полному заполнению младших разрядов 9 счетчика 8, на значение сигналов на шинах 12 непосредственно снимается с шин 12, так как полное заполнение младших разрядов 9 счетчика 8 соответствует умножению входных сигналов на 100 или сдвигу сигналов шин 12 на две декады.

На фиг. 2 приведены цифровые линейно нарастающие сигналы К на выходе

Устройство цифрового задания трехфазного напряжения, содержашее счетчик импульсов, вход которого соединен с шиной стабильной частоты, реверсивный счетчик импульсов, вход которого соединен с шиной задания частоты выходного напряжения, блок умножения, первый вход которого соединен с входными ши-нами цифрового задания величины выходногО нвнряжения, и логический блок, отличающееся тем,что,с целью повышения точности, помехоэашищенности и надежности, в него введены три блока сравнения, выходы которых соединены с первым, вторым и третьим входами логического блока соответственно, первые входы первого и второго блоков сравнения соединены с прямым и обратным выходами блока умножения, а первый вход третьего блока сравнения соединен с шиной цифрового задания величины выходного напряжения, а вторые входы всех блоков сравнения соединены с выходом очетчикв импульсов, причем выходы младших разрядов реверсивного счетчика соединены со вторым входом блока умножения, а выходы старшего трехфазного разряда этого счетчике соединены с четвертым, пятым и шестым входами логического блока, выходы которого соединены с шинами выходного сиг нала./

Источники информации, принятые во внимание при экспертизе:

1. Патент США N 3 704 403, .кл. 318-227, 23.02.1972.

2. Патент Великобритании

% 1 190847 кл. Н 2 %, 06.05.1970.

5 6210 счетчика 2, линейно нарастающие сигналы.Ь на прямых выходах блоках 11 линейно спадающие сигналы М)на обратных выходах блока 11 и постояйные сигналы

К, соответствуюшие сдвинутым на две декады сигналам шин 12.

-3a время заполнения счетчика 8 счетчик 2 многократно заполняется и возвращается в исходное состояние от импульсов стабильной частоты.

B блоке 3 происходит сравнение цифро- вых сигналов К и 1, в блоке 4 — сиг, налов К и М, в блоке 5 - сигналов К и Ц . Если сигналы K становятся меньше соответствуюших сигналов на первых. входах блоков сравнения 3, 4 и 5, нв их выходах появляются соответственно импульсы напряжений U U 13 >.

Значения широтно-модулированных сигналов 0 g, 6 g, U определяются сигналом на шинах 12.

При работе счетчика S в рехйме вычитания импульсов сигналы на прямых и обратных выходах блока 11 меняютая местами, что приводит к смене выходных сигналов между блоками 3 и 4.

При цифре 0 на выходах старших ., разрядов 10 счетчика 8 блок 6 пропус-, кает напряжение lJ -положительной aoiлярности на шину 13 (фаза A)>Up- положительной полярности на шину 15 (фа

30 эа С), 0 «отрицательной полярности на шину 14 (фаза В).

При цифре "1" на выходах старших разрядов -10 счетчика 8 блок 6 пропускает напряжение U1 -отрицательной по

3$

) лярности на шину 15, U2 -отрицатель ной полярности на шину 14,U - положительной полярности на шину 13.

При цифре 2 нв выходах старших разрядов 10 счетчика 8 блок 6 пропус46 кает напряжение U 1 -положительной полярности на шину 14, Q< -положительной полярности на шину 13,Юь -отрицательной полярности на шину 15.

При цифрах "3"; "4", 5" напряже- 45 ния U 1 U Ug пропускаются нв шины 13, 14 и 15 аналогично цифрам

«О «1 "2 но имеют противоположиую им полярность»

Таким образом, нв шинах выходного сигнала 13, 14, 15 устройства появляются трехфазные напряжения с формой, близкой к синусоидальному закону широт- но-импульсной модуляции, величина которых пропорциональна входному сигналу, а порядок чередования фаз определяется режимом работы реверсивного,счетчика..

Частота этого нвлряжения линейно связана с частотой импульсов, поступаюших на вход реверсивного счетчика.

Все преобразования в устройстве выполняются в дискретном виде и возможна полнея реализация схемы в интегральном исполнении, в частности нв БИС с инжек» ционным питанием.

Формула изобретения