Анализатор сигнала тактовой синхронизации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Сои1напнстнчесин х

Республик (») 621112

t.-, 1 Ь

4g-- ô„ 1 Ф Й(Й (61) Дополнительное к авт. свид-ву— (22) Заявлено 110377(21) 2461796/18-09 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 250878.Бюллетень № 31 (45) Дата опубли кования описания 1 4 0 77 8 (51) М. Кл. н 04 1, 7/02

Государственный комитет

Совета Министров СССР оо делам иаобретений н открытий (53) УДК 621.394.662 (088.8) (72) Авторы изобретения

И.Е. Байдан, В.В. Гинзбург, А ° А. Гришуков, В.A.Äàíèëåâñêèé, В.С.Караваев, 10.A.Ïàâëè÷åHêo и Л.N.Ðàõoâè÷ (71) Заявитель (54) АНАЛИЗАТОР СИГНАЛА ТАКТОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к связи и может использоватьая в многоканальных модемах с фаэоразностной модуляцией.

Известен анализатор сигнала так- о товой синхронизации, содержащий объединенные по входу два основных измерителя переходных помех и два дополнительных измерителя переходных помех, причем выходы двух основных измери- 10 телей переходных помех через вычитающий блок подключены к входу интегратора, а также переключатель режима работ (11 .

Однако известный анализатор имеет lо ограничение по скорости вхождения в синхронизм.

Цель изобретения -. сокращение времени вхождения в синхронизм.

Для этого в анализатор сигнала 20 тактовой синхронизации, содержащий объединенные по входу два основных измерителя. переходных помех и два дополнительных измерителя переходных помех, причем выходы двух основных . 25 измерителей переходных помех через вычитающий блок поцключены к входу интегратора, а также переключатель режима работ, введены блок определения зоны границ посылок и последова- 30 тельно соединенные блок добавления исключения импульсов, управляемяй опорным генератором, и делитель частоты, при этом выходы основных и дополнительных измерителей переходных помех через блок определения эоны границ посылок подключены к входам переключателя режима работ, выходы которого подключены к управляющим входам делителя частоты, выходы разрядов которого подключены к управляющим входам переключателя режима работ, кроме того, выход интегратора подключен к входу блока добавленияисключения импульсов.

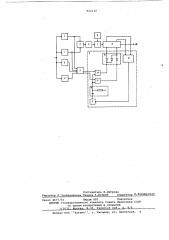

На чертеже дана структурная электрическая схема предлагаемого анализатора °

Анализатор сигнала тактовой синхронизации содержит объединенные по входу два основных измерителя 1 переходных помех и два дополнительных измерителя 2 переходных помех, причем выходы двух основных измерителей 1 через вычитающий блок 3 подключены к входу интегратора 4, а также переключатель 5 режима работ. Анализатор содержит также блок 6 определения зоны границ посылок и после,довательно соединенные блок 7 добав-, 621112. ления-исключения импульсов, управляемый опорным генератором 8, и де,литель 9 частоты, при этом выходы основных и дополнительных измерителей 1 и 2 соответственно через блок 6 подключены к входам переключателя 5, выходы которого подключены к управляющим входам делителя 9 частоты, выходы разрядов которого подключены к управ» ляющим входам переключателя 5, кроме того, выход интегратора 4 подключен к входу блока 7.

Переключатель 5 представлен в виде соединенных между собой дешифратора 10, ждущего мультивибратора 11, формирователя 12 короткого импульса, элементов 13 совпадения и шифратора 14 причем управляющие входы переключателя 5 являются входами дешифратора

10, входы переключателя 5 являются входами элементов 13 совпадения, а выходы переключателя 5 являются выходами шифратора 14. Выходом аналиэа° тора является выход делителя 9 час70ТЫАнализатор работает следующим образом.

Когда тактовый синхронизм не нарушен, фаза границ посылок находится в зоне стационарной работы и, так как наименьший уровень сигнала при этом имеет место на выходах основных измерителей 1, на всех выходах блока 6, подключенных к входам переключателя 5, устанавливается низкий

ПОтенциал. Подстройка фазы границ посылок при этом выполняется только основными измерителями 1, выходные напряжения которых после вычитания в вычитающем блоке 3 и усреднения в интеграторе 4 поступают в блок 7, где и осуществляется соответствующая коррекция. При такой подстройке фаза границ посылок корректируется достаточно плавно, так как каждое добавление или исключение импульса происходит на входе делителя 9 частоты, а тактовые импульсы (выделенные границы посылок) снимаются с его выхода.

Если границы посылок приходящих сигналов окажутся вне зоны синхрониэма, то на одном из выходов блока 6 появится положительный потенциал . При этом порядковый номер этого выхода указывает зону, в которой находятся границы посылок. Далее, при первом

3б

ЯО же обнулении делителя 9 частоты на выходе дешифратора 10 формируется импульс, запускающий ждущий мультивибратор 11, выходной импульс которого через формирователь 12 поступает на входы элементов 13 совпадения. На выходе элемента 13 совпадения, соответствующего указанной зоне, формируется короткий положительный импульс. Этот импульс через шифратор 14 устанавливает в единичное состояние определенные ячейки делителя 9 частоты, чтобы тактовый импульс синхронизации (граница посылки) попал в зону стационарной работы. Происходит скачкообразный перевод фазы грЪниц посылок из областей больших расстроен в зону стационарной работы.

Предлагаеьый анализатор позволяет уменьшить время вхождения в синхрониэм без ухудшения помехоустойчиво-сти.

Формула. изобретения

Анализатор сигнала тактовой синхронизации, содержащий объединенные по входу два основных измерителя переходных помех и два дополнительных, измерителя переходных помех, причем

0 выходы двух основных измерителей переходных помех через вычитающий блок подключены к входу интегратора, а также переключатель режима работ, отличающийся тем, что, с целью сокращения, времени вхождения в синхрониэм, введены блок определения зоны границ посылок и последовательно соединенные блок добавленияисключения импульсов, управляемый опорным генератором, и делитель частоты, при этом выходы основных н дополнительных измерителей переходных помех .через блок определения зоны границ посылок подключены к входам переключателя режима работ, вы48 ходы которого подключены к управляющим входам делителя частоты, выходы разрядов которого подключены к управляющим входам переключателя режима работ, кроме того, выход ннтегра50 тора подключен к входу блока добавлени я-и сключени я импул ьсо в .

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР 9 496688, кл. Н 04 L 7/02, 1974.

621112

Составитель Е.Петрова

Редактор Л.гребенникова Тех е А.Богдан Ко екто " ° "цемирская

Заказ 4677/53 Тираж 805 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра ская наб. . 4 5

Филиал ППП Патент, г. Ужгород, ул. Проектная, . 4