Устройство для преобразования позиционного десятичного кода в двоичный код

Иллюстрации

Показать всеРеферат

ОПИСАН Й Е

ИЗОБРЕТЕНИЯ (Yi)622075

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 10.01.77 (21) 2443014/18-24 с присоединением заявки № (23) Приоритет (51) М. Кл G 06F

5/02

Государственный комнтег

Совета Министров СССР по делам изобретений и открытий (43) Опубликовано 30.08.78. Бюллетень № 32 (53) УДК 681.325 (088.8) (45) Дата опубликования описания 31.07.78 (72) Авторы изобретения

Н. А. Подколзина и А. 3. Подколзин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ПОЗИЦИОННОГО ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ

КОД

Изобретение относится к области вычислительной техники и может быть использовано в цифровых системах автоматического управления.

Известны быстродействующие устройства для преобразования целых и дробных десятичных чисел в двоичную систему счисления (1), содержащие сумматор, двоичный регистр и линии задержки. Недостатком таких устройств является большая сложность.

Наиболее близким к изобретению является устройство (2) для преобразования позиционного десятичного кода в двоичный код, содержащее шифратор десятичного кода, двоично-десятичный регистр дешифратор двоично-десятичного кода. Недостатком устройства являются значительные аппаратурные затраты.

Цель изобретения — упрощение устройства.

Достигается это тем, что в устройство введены генератор одиночных последовательностей импульсов, коммутатор тетрад, элементы ИЛИ, двоичный накапливающий счетчик, разрядные входы которого через элемент ИЛИ соединены с соответствующими выходами шифраторов двоичного кода, входы второй группы. которых подключены к выходам генератора одиночных последовательностей импульсов, а третьи входы шифраторов двоичного кода соединены с соответствующими выходами коммутатора тетрад, управляющий вход которого соединен с управляющим выходом генератора одиночных последовательностей импульсов, информационный вход которого через элемент ИЛИ подключен к информационным входам устройства, а управляющие входы—

10 к тактовым шинам устройства, выходы двоичного накапливающего счетчика являются выходами устройства.

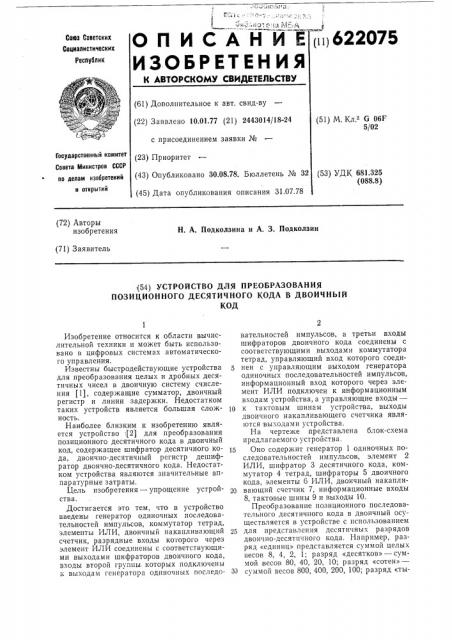

На чертеже представлена блок-схема предлагаемого устройства.

15 Оно содержит генератор 1 одиночных последовательностей импульсов, элемент 2

ИЛИ, шифратор 3 десятичного кода, коммутатор 4 тетрад, шифраторы 5 двоичного кода, элементы 6 ИЛИ, двоичный накапли20 вающий счетчик 7, информационные входы

8, тактовые шины 9 и выходы 10.

Преобразование позиционного последовательного десятичного кода в двоичный осуществляется в устройстве с использованием

25 для представления десятичных разрядов двоична-десятичного кода. Например, разряд «единиц» представляется суммой целых весов 8, 4, 2, 1; разряд «десятко⻠— суммой весов 80, 40, 20, 10; разряд «сотен»вЂ”

Зо суммой весов 800, 400, 200, 100; разряд «тыО22078

50

60

3 сяч» — суммой весов 8000, 4000, 2000, 1000 и т. д., разряд «десятых» — суммой дробных весов 0,8, 0,4, 0,2, 0,1; разряд «сотых» — суммой дробных весов 0,08, 0,04, 0,02, 0,01; разряд «тысячных» — суммой дробных весов 0,008, 0,004, 0,002, 0,001 и т, д.

В процессе преобразования названные веса заменяются двоичными эквивалентами, причем дробная часть десятичного числа, представляемая суммой дробных весов, переводится в двоичную систему с определенной заданной точностью.

Перед началом преобразования накапливающий двоичный счетчик и коммутатор тетрад устанавливаются в нулевое состояние. Преобразование последовательного десятичного кода начинается со старшего разряда. На соответствующую старшему разряду десятичного кода входную шину 8 подается потенциальный сигнал, поступающий через элемент ИЛИ 2 на управляющий вход генератора 1 и на шифратор 3 кода

«8421». По ближайшему тактовому импульту Ть поступающему на шину 9, с первого разряда генератора 1 подается импульс, устанавливающий первый разряд коммутатора 4 тетрад в состояние «1». При этом сигнал с выхода первого разряда коммутатора поступает на управляющий вход шифратора двоичного кода, соответствующего старшему разряду десятичного кода. Старший разряд десятичного кода, представляемый тетрадой двоичных разрядов, в шифраторе двоичного.кода, преобразуется в двоичный код: вначале преобразуется старший весовой разряд тетрады (разрешением служит импульсный сигнал, поступающий по очередному тактовому импульсу с выхода второго разряда генератора 1), затем преобразуется второй весовой, разряд тетрады (разрешением является импульсный сигнал, поступающий по очередному тактовому импульсу, с выхода третьего разряда генератора 1 и т. д. Двоичные эквиваленты с выходов выбранного шифратора двоичного кода поступают через элементы ИЛИ 6 на входы двоичного накапливающего счетчика 7. Вслед за старшим разрядом десятичного кода преобразуется очередной десятичный разряд. Потенциальный сигнал с соответствующей входной шины поступает через элемент ИЛИ 2 на управляющий вход генератора 1 и на шифратор 3 кода

«8421». По ближайшему тактовому импульсу с первого разряда генератора 1 поступает импульс, устанавливающий второй разряд коммутатора 4 тетрад в состояние

«1». При этом сигнал с выхода второго разряда коммутатора подается на управляющий вход нового шифратора двоичного кода, соответствующего очередному десятичному разряду. С помощью этого шифратора тетрада очередного десятичного разряда

45 преобразуется в двоичный код так уке, как

И старшИй разряд десятичного кода и т. д.

Накопленный в счетчике 7 двоичный эквивалент преобразуемого десятичного числа поступает на выходные шины 10.

Для обеспечения надежной работы устройства необходимо соблюдать следующее соотношение для выбора длительности тактирующих сигналов Т:

0,01

-.. с, и где n — суммарное число двоичных эквивалентов на выходе шифратора двоичного кода, соответствующего старшему разряду переводимого десятичного числа.

Достоинствами предлагаемого устройства являются простота преобразования десятичных целых и дробных чисел в двоичную систему счисления, что достигается введением двоичного накапливающего счетчика, и простота схемы управления, состоящей из генератора одиночных последовательностей импульсов и коммутатора тетрад.

Формула изобретения

Устройство для преобразования позиционного десятичного кода в двоичный код, содержащее шифратор десятичного кода и и шифраторов двоичного кода, входы первой группы каждого из которых соединены с соответствующими выходами шифратора десятичного кода, входы которого подключены к информационным входам устройства, отличающееся тем, что, с целью упрощения устройства, в него введены генератор одиночных последовательностей импульсов, коммутатор тетрад, элементы

ИЛИ, двоичный накапливающий счетчик, разрядные входы которого через элементы

ИЛИ соединены с соответствующими выходами шифраторов двоичного кода, входы второй группы которых подключены к выходам генератора одиночных последовательностей импульсов, а третьи входы шифраторов двоичного кода соединены с соответствующими выходами коммутатора тетрад, управляющий вход которого соединен с управляющим выходом генератора одиночных последовательностей импульсов, информационный вход которого через элемент

ИЛИ подключен к информационным входам устройства, а управляющие входы — к тактовым шинам устройства, выходы двоичного накапливающего счетчика являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3185825, кл. 235 — 155, 1965.

2. Авторское свидетельство СССР № 230514, кл. G 06F 5/2, 1968.

1 .

Редактор Н. Громов

Заказ 1465/6 Изд. № 572 Тираж 799

НП0 Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Я-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2

Составитель Н. Шелобанова

Техред А. Камышникова

Корректоры Е Хмелева и Н Федорова