Устройство для возведения п-разрядных чисел в квадрат

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союэ Советских

Сециапистичесии к

Респубпии

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено Зм2.75.(21) 2310614/18-24 с присоединением заявки М (23) Приоритет (43) Опубликовано 050978,Бюллетень М 33 (45) Лата опубликования описания 240778 (St)--¹ Кл.

Q 06 F 7/38

Государственный комитет

Совета Nwscrpoe СССР

00 деяам изобретений н открытий (53) УДК 681.327 (088. 8) (72) Авторы изобретения

A.Â.Èàêååâ и В.A.×åðêàñîç (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ (1 -РАЗРЯДНЫХ ЧИСЕЛ

В КВАДРАТ

Изобретение относится к области вычислительной техники, в частности к устройствам цифровой обработки радиолокационной информации.

Известны устройства для возведения чисел в квадрат, содержащие счетчики, элементы задержки и элементы И, ИЛИ (13.

Яедостатком нх является сложность, Наиболее близким техническим реше- 1О кием к изобретению является устройство для возведения и -разрядных чисел в квадрат, .содержащее и -разрядный входной регистр, разрядные выходы которого соединены со входами нечетных разрядов 2h-разрядного выходного сумматора и (П -l) группу элементов И по элементов И в каждой (где 1 — номер группы). Разрядные входы входного регистра соединены с шинами входного кода, выход каждого разряда входного регистра подключен ко входу одноименного элемента И всех rpyrrn(2).

Яедостатком этого устройства является низкое быстродействие.

Целью изобретения является повианние быстродействия устройства.

Эта цель достигается тем, что предложенное устройство содержит (2 и -5) группы комбинационных сумматоров (и > 6) . Входы группы комбинационных сумматоров, выход которой соединен с К -ым разрядом выходного сумматора (где К 1 - 2 П ), соединены с выходами элементов И, которые имеют весовой коэффициент К= л+ (где п и j — номера разрядов входного регистра), а выходы которых соединены со входами этих же элементов И. Вход группы комбинационных сумматоров К -го разряда соединен с выходом переноса групгы комбинационных сумматоров (К вЂ” 1) разряда.

Выход каждого f-го (g-"1 4 П ) разряда входного регистра соединен со входами всех (g --l) элементов И груп пы (f -1) разряда.

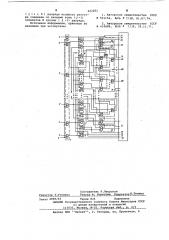

Структурная схема предлагаемого устройства приведена на чертеже.

Единичные входы разрядов регистра

1 соединены с шинами 2 входного кода, а нулевые — с шиной 3 установки в нуль . Группы 4-8 элементов И содержат соответственно 1,2 и т.д. до (A """l) 7 элементов И 9 в группе. Выходы каждого разряда регистра 1 подключены к одноименным элементам И всех групп и к остальным элементам и группы предыдущего разряда. Единичные выходы всех разрядов регистра 1 соединены со входами нечетных разрядов выи

623201 ходного сумматора. При этом выход первого разряда .регистра 1 соединен

<со входом 10, являющимся одним иэ входов первого разряда выходного су атора, выход триггера второго разряда регистра 1 — co входом 11, являющимся одним иэ входов третьего разряда выходного сумматора, выход третьего разряда регистра 1 — со входом 12, являющимся одним из входов пятого разряда выходного сумматора и т,д.

Выход (И -1 )- ro разряда регистра 10

1 соединен со входом 13, являющимся одним из входов (2 Л "3)-го разряда выходного сумматора, а выход И -го разряда регистра 1 — co входом 14, являющимся одним из входов (2 р -1)»ro l5 разряда выходного сумматора. Выход элемента И 9 группы 4,относящийся к первому разряду регистра 1, соединен со, входом 15,являющимся другим входом третьего разряда выходного сумматора, 20 выходы элементов И группы 5, относящейся ко второму разряду регистра 1со входом 16 четвертого разряда выходного сумматора и со входом комбинационного сумматора 17 группы 18 и т.д. Выходы элементов И группы (-1)ro разряда регистра 1 соединены со входами групп комбинационных сумматоров, выходы которых соединены с (2 1

-1), (2 -2), (П-1) разрядами выходного сумматора. Выходы элементов И 9 группы 8, относящейся к (й -1)-му разряду регистра 1, соединены со входами групп 19-22 комбинационных сум, маторов, выходы которых соединены со входами 23 - 26, (2.И -1), (2 п -2) до (П+ 1 ) разрядов выходного сумматора.

Выходы переносов из группы,комбинационных сумматоров, выход которой соединен с К -ым разрядом выходного сум- 40 матора, соединены со входами группы сумматоров 17, выход которой соединен с (К+ 1) -йм разрядом выходного сумма тора. Выход переноса из последней группы 22 сумматоров 17 соединен со 45 входом 27 старшего разряда выходного сумматора 28.

Устройство работает следующим образом.

Перед записью двоичного кода на 50 регистр 1 все разряды последнего обнуляются импульсом установки в нуль, поступающим по шине 3. Записанный на регистр двоичный код можно представить как сумму значений (О или 55

1) разрядов, умноженных на свой весо вой коэффициент, определяемый номером разряда, ° Г Х Z(5-1 )

Р1

1

60 а после возведения числа в квадрат имеем две суммы: и-1 О (. -1

1=

К=1 к=

Щ с +/

Первая сумма в устройстве реалиэу|ется путем соединения выходов всех разрядов и -разрядного регистра 1 со входами (10-14) нечетных разрядов 2Празрядного выходного сумматора, а вторая сумма (сумма удвоенных произведений) реализуется на группах 4-8 схем

И и группах 18-22 комбинационных сумматоров. При этом на выходе любогоэлемента И имеем сигнал, соответствующий произведению Х>.Х,который подается на вход комбинациойного сумматора той группы, выход которой соедйнен со входом К-го разряда выходного сумматора, (где К * tn+j). Например, на втором элементе И группы 5 образуется частное удвоенное произведение )(Х 2

2 з второго и третьего разрядов входноге регистра, поэтому сигнал с выхода этого элемента И поступает на вход группы 18 сумматор 17, так как последняя . относится к пятому разрядуУ 2 4 выходного сумматора (один и тот же весовой коэффициент). Квадраты первого и третьего разрядов входного регистра а о а

Х „2 и Х з 2 поступают на входы 1-ro и 5-го разрядов 10,12 выходного сумматора, так как У„ 2 и У» 2 . Таким образом, после записи кода во входной регистр, спус тя время, необходимое на прохождение сигнала по самой длинной цепочке схем И, комбинационных сумматоров и выхсдного сумматора, на выходном сумматоре образуется результат ° формула изобретения устройство для возведения и-разрядных чисел в квадрат, содержащее И— разрядный входной регистр, разрядные выходы которого соединены со входами нечетных разрядов 2 П -разрядного выходного сумматора, разрядные входы входного регистра соединены с шинами входного кода,(Й вЂ” 1) группу элементов И по 1 элементов И в каждой, где -номер группы, причем выход каждого разряда входного регистра подключен ко входу одноименного элемента И всех групп, о т л и ч а ю щ е е с я тем, что; с целью повышения быстродействия оно содержит (2 И -5) (П > б) груПпы комбинационных сумматоров, входы группы комбинационных сумматоров, выход которой соединен с К-ым разря-. дом выходного сумматора (где К= 1-;2 п ) соединены с выходами элементов И,,;оторыз имеют весовой коэффициентК=а1, (где tn u j - номера разрядов вхсднсгс регистра), а выходы которых соединены со входами этих же элементов И, вход группы комбинационных сумматоров k-ro разряда соединен с выходом переноса группы комбинационных сумматоров (Х -1) разряда, выход каждого -ro

Ь 623201 (J 1 -: П ) Разряда входного регистра соединен со входами всех (j -1) элементов И группы (М -1) разряда.

Источники информации, принятые во внимание при экспертизе:

1, Авторское свидетельство СССР

9 531152, 506 F 7/38, 01.07.74.

2. Авторское свидетельство СССР

Р .419888, 606 Г 7/38, 29.11,71.. I

Составитель Р.Яворская

Техред М. Борисова Корректор H.ТУпица

Редактор Л.утехина

А ь с л Патент, г. Ужгород, ул. Проектная, 4

Филиал ППП

Эаказ 4909/45 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета. Министров СССР пэ делам изобретений и открытий

113035 Москва Ж-35 Раушская наб. д. 4/5