Устройство для вычисления модуля комплексного числа

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советсннх

Соцнавнстнческнх

Респубпнн т о,1н .,,.," (11) б23202

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву-, (22) Заявлено 291276 (21) 2435330/18-24 с присоединением заявка,йз (23) Приоритет (43} Опубликовано 050978. Бюллетень лз 33 (45) Дата опубликования описания 24,07.78

{И) М. Кл.

906 Г 7/38

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (S3} УДК 681.327 (088 ° 8) Г.Д.Бахтиаров и Т.E.Øàõ (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ

КОИПЛЕКСНО1"О ЧИСЛА

Изобретение относится к областивычислительной техники н может найти применение в специализированных вычислителях, например цифровых Фильтрах, оперирунщих с комплексными числами.

Известно специализированное арифметическое устройство для операций с комплексными числаии,,которое содержит регистры памяти, блок управления; формирователи поразрядных произведе- - Ю ний н набор накапливающих комбинационных сумматоров (11 . Оно может быть использовано для вычисления модуля.

Недостатком этого устройства является значительный объем аппаратуры.

Известно также уст йство для вычисления функции Z= хе+те, содержащее два регистра, два сумматора, элементы

HE элемент задержки и квадратор (2J.

Его недостатком является невысокое бЫ,тродействие,которое определяется

Мислом требуемых в процессе вычисления модуля приближений,определяемых раз= .рядностью входной информации и соотнОшением между известным Х н искомым 3, Целью изобретения является повышение быстродействия устройства.

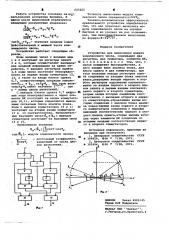

Поставленная цель достигается тем, что в предложенное устройство введен блок анализа знака, два блока сдвига и два коммутатора. Знаковые выходы регистров памяти соединены со входами блока анализа знака. Разрядные выхсщы первого и второго регистров нодключены соответственйо ко входам первого и второго блоков сдвига и первым входам соответственно первого и второго сумматоров, вторые входи которых соединены соответственно с выходами второго и первого коммутаторов, управляющие входы последних соединены с выходом блока анализа знака.. Первые входы первого и второго коммутаторов соединены с первыми выходами соответственно первого и второго блоков сдвига, вторые выходы которых через элементы

НЕ соединены со вторыми входами соответственно первого и второго коммутаторов.

На фнг. 1 дана структурная схема устройстват на фиг. 2 — векторная диаграмма.

Устройство содержит, входные шины

1 н 2, регистры памяти 3 и 4, блок анализа знака 5, два блока сдвига 6 и 7, элементы НЕ 8 и 9, два коммутатора 10 и 11, два сумматора 12 и 13, которые .соединены с выходными шинами 14 и 15.

623202

Точность вычисления модуля комплексного числа определяется со> P„, Технико-. зкономическая .эффективность предлагаемого устройства определяется тем, что оно позволяет вычислить модуль комплексного числа на порядок э быстрее и во столько же раз экономичнее, чем непос едственное вычисление по формуле Хи Х l .

Формула изобретения

Работа устройства основана на Ис1

; пользовании алгоритма Волдера. В едиом цикле вычислений реализуются еаедующие рекурентные уравненияг

Ф ееэ%„ щк ™а„-„ Ъ „,trqkrmet)„ 4 щ,- значения входных кодов действительной и мнимой части ком- йлеКсиого числа.

Устройство работает следующим образом.

Ходы входных чисел с входных акать

1 и 2 поступают иа регистры памяти

3 и 4, которые осуществляют эапомина- 18 ние входной информации на время обработки. С выходов регистров памяти

3,4 коды чисел поступают непосредственно;на первые входы сумматоров 12, l3 а также на входы блоков сдвига

6,7, осуществляющих операцию умножения(9к, и t) „наФдЧ„. При этом вели- чиныФ гМ„имеют значение 2 ", где к — номер цикла вычислений.

С:выходов блоков сдвига 67 цифро- 25 вые коды непосредственно и через элементы НЕ поступают на входы коммутатоpos 10,11 которые управляются выходными сигналами блока анализа знака.

Коды с выходов коммутаторов 10 и 11 30 поступают на вторые входы сумматоров

13 и 12 соответственно. Вычислительные значения чисел д» и.5„с выходов сумматоров поступают на выходные шины

l4 и 15 ° 35

Вычисленное значение к

0 /Я J/ П Сов Р созе

К о /1в гдето J - модуль комплексного числау

1 40 постоянный коэффициент, цссВЧ„ вависищил св числа ции-. лов вычислений.

Устройство для вычисления модуля комплексного числа, содержащее два регистра, два сумматора, элементы НЕ, о т л и ч а ю-щ е е с я тем, что, с целью повышения быстродействия, в него введен блок анализа знака, два блока сдвига и два коммутатора, при этом знаковые выходы регистров памяти соединены со входами блока анализа знака,разрядные выходы первого и вто-. рого регистров подключенй соответст-. венно ко входам первого и второго блоков сдвига и первым входам соответственно первого и второго сумматоров, вторые входы которых соединены соответственно с выходами второго и первого коммутаторов, управляющие входы которых соединены с выходом блока авали за энака1первые входы первого и второго коммутаторов соединены с первыми выходами соответственно первого и вто» рого блоков сдвига, вторые выходы которых через Элементы HE соединены со вторыми входами соответственно первого н второго коммутаторов.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

9 399859, 606 F 7/38 1971.

2 Авторское свидетельство СССР

В 392494 6 06 F 7/.38, 1971.

ЦИИИПИ Заказ 4909/45

Тири 826 Подписное

Филиал ППП Патент, г.Ужгород,ул.Проектная,4