Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

О П И Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Ресвубпик (11)623260

И АВТОРСКОМУ СВИДЙТИЛЬСТВУ (61) Дополнительное к авт, свил-ву(22) Заявлено 08.02.77 (21) 2451200/18-09 с присоединением заявки № (23) Приоритет(43) Опубликовано05.09.78,Бюллетень № 3 (45) Дата опубликования описания В. в .18

2 (51) М. Кл.

Н 04 L 7/08

Гасударственный нанитет

Сввета йннивтрвв СЮ аа делан нввбретений и етнрытнй (53) УДК 621.394. .662.2 (088.8) (72) Авторы изобретения

A. П. Баев и М. И. Круш

Одесский отдел центрального научно-исследовательского института связи (71) Заявитель (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

Изобретение . относится к электросвязи

И МОЖЕТ ИСПОЛЬЗОВаТЬСЯ В ЦнфРОВЫХ СИСТЕмах передачи.

Известно устройство цикловой синхронизации, содержа1цее последовательно соединенные регистр сдвига, дешифратор, пер- 5 вый анализатор, первый накопитель, блок совпадения и генератор, выход которого подключен к другому входу первого анализатора, другой выход которого через вт рой накопитель по,:1ключен к другому Входу первого накопителя, а также последовател1,—

10 но соединенные второй анализатор, блок управления и делитель, выход которого подкл1очен ко второму входу блока совпадения и первому входу второго анализатора. а другой вход делителя объединен со входом регистра сдвига и другим входом генератора и является входом устройства, причем выход дешифратора подключен к второму входу второго анализатора 1J.

Однако такое устройство не обеспечивает достаточной помехоустойчивости.

11ель изобретения — — повышение помехоустойчивости и сокращение времени вхождения в синхронизм.

Для этОГО В устроистВО циклОВОи синхронизации, содержащее последовательно соединенные регистр сдвига, дешифратор, первый анализатор, первый накопитель, блок со1зпадения и генератор, выход которого подключен к другому входу первого анализатора, другой выход которого через второй накопитель подключен к другому входу первого накопителя, а также последовательно соединенные второй анализатор, блок управления и делитель, выход которого подключен ко второму входу блока совпадения и первому входу второго анализатора, а другой вход делителя объединен со входом регистра сдвига и другим входом генератора и является входом устройства, причем выход дешифратора подключен к второму входу второго а нализатора, введен дополнительный накопитель, вход которого соединен с выходом делителя, а выход — с третьим входом блока совпадения.

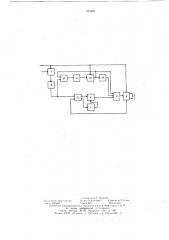

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство цикловой синхронизации содержит последовательно соединенные регистр 1 сдвига, дешифратор 2, первый анализатор 3, первый накопитель 4, блок 5 совпадения и генератор 6, выход которого

628260 подключен к другому входу 1!срво(î ill(!, !iзатора 3, 1ругой «ы>«)д которого через B:»j)OH H3KOIIHT(>ЛЬ / I «), if< lO×(>kl К ДР>>>ГО \ «Х» дх первого пак(н!Итсля 4, 3 также послс10ватсльно сосд !Неfll!I>tc втор»Й ан;lk«içàòoð 8, 5 блок 9 управ.«!!II« и,целитель 10, выход к»ГОР»ГО ПОД!(, К)Ч< It КО В! ОРОМ > «\»1\ <>ЛОк;1 5 совпадения и пер«ому входу 13T»p<>l ( анализатора 8. 3 (ругой в од 1елитсля !О соединен со входом регистра сдвига и другим входом генератора 6 и является входом устройства, причем выход le!lift(j>pktTop2 2 подклгочеH к второму входу второго анализатора 8, а также;Iîïîëíèòcëüíûé накопитель 11, вход "оторого сое Ltllicfl с выходом делителя 10, а выхо1 — с треты(м входом 15 блока 5 совпадения.

Устройство раоотает еле (уюгцим образох!.

Б состо>!«kf fl си нхронизм (! си Гнал ы Н3 «ыхо,:гс деп!ифратора 2 и генератора 9 co«f12;!31»т по «рсмени. 1lри этом на выходе пер20 в(>го анализ tTopd 3 период!>чески появляк>гся сигналы, заполня)ощ!Ге второй пак<>пптель 7. а пер«ый накопитель 4 опуcT»I!I(. II.

На Выходе ()„ !OK2 !) СО«паДенпи (ltl нал»Iсутствуст, и ге1«р !Тоp 6 р;1(тотас! Сlliixj)<>fi-!

lo c принимаемым гpi lilt»«t, сигнал» ii.. 1(. лн.гель 10 раоотает синхро! Ио с гснергг!»ром 6. сигналы на «ыходс «I »j)ofo анализатора 8 и на выходе блока 9 упра«лсния отсутствуют.

Г1ри нарх шенин сипхронизма сигна thl ll3 30 входах анализаторо« 8 ll 8 не синфазны

Н3 BhlXO 13 X ЭТИХ 3Н(1,11133TOp013 НОЯВлЯюТся сипlалы H(совпадения. Сигналы несовпа.1енпя с выхода первого анализатора 8 поступают llà Bxo„f, первого накопителя 4 и наполняк)т его. После наполнения первого накопителя 4 на его выходе появляется сигН2,7, по 1ГОТ3 В. Ill«et IO!II« H Олок 5 СОВ П3ДСII It H к >.cT(tffo«f генератора 6. ! Iервый сигнал несовпадения на вых(> гс лв

l3 I < l>OI0 ktIl3,1Из3Т0р 1 8 IIOJI OT313лиВ3 T

<>.!Ок 9 уира«7епия к установке делителя 10. ! !ри 1юявлс>ши на выходе де)пифратора 2 сл)гнала I3 выходах первого ан31ltзатоj)d 8 и бл»ка 9 управления появляются сп-палы, мстанавливающие делитель 10.

Д3лее усl ройство переходит в p(жим к»нтр»ля. в котор(>м оно находится .Io т(х lioð, ш>ка;13 анали !руемой позиции не c(!>Oj)xll!j)x ется комбинац)1Я ctlx! f3010Â, QT1IIт go

cинхрогруппы. Гlосле этого следуloIIUllf сlli -!

Гал на B»ix01c дешифратора 2 уст ill»i«t делитель 10 и устройство персидет в режим к»п1р<) 1я си нх ропп:331(! t 3 дру! ОЙ пози пи и

lit)Il! Ill)i3p.мого I j)vl1t10i30I о сигнала.

Г,!Ким образом осуществляется процесс

II»1«K(1 cHHxpocHI í3,7(i незаВисимо QT сОстОя

IIHH первого накопителя 4.

11cðåñòðîéêà генератора 6 производится только после обнаружения устойчивого отсу!сг!3ия состояния сипхронизма на преды*s fItcIf .тактовой позиции (после заполнешlЯ IlcpB»f o накопи Г(,!Я 4 по Выходу из

Gkt i I x f) 0 f I It 3 i3t 3 j и x c ò <7 It "I f i в 0 Г 0 0 б н а р у )к е !1 и я синхрогруппы на дряз гой позиции. (После заполнения дополнительного накопителя 1! по входу «синхронизх!1.

В предлата(мом устройстве цикловой синxj)ollfl«3lfltH исключается ложная перестройка генератора б, и, как следствие, время несинхронной работы аппаратуры.

coKj)3tu3eTcH. 1Х()>ффициент деления допол-!!Итсльного накопителя 1! выбирается исхо1Н из статических характеристик групповоГо сигнала и структуры синхрогруппы.

При использовании предложенного устрой Т«3 значительно повышается помехоустойчивость и сокра!цается время вхождения в синхронизм.

Фор.>гг)э га ггзооретения

Устройство цикловой синхронизации, содержащее г«>следовательно соединенные регистр cдвига, деп!Пфратор, первый анализат<>р, первый накопитель, блок совпадения и генератор, выход которого йодключен к друГ» , входу первого анализатора, другой

ВЫ хг»д КОтОрОГО Ч«рЕЗ ВтОрОй НаКОПИтЕЛЬ подключен к друtoxth входу первого накопителя, а также последовательно соединенные второй анализатор, блок управления и делитель, выход которого подключен ко второму входу блока совпадения и первому

t3xo.7х второго анализатора, а другой вход делителя об.ьсдинен со входом регистра сдвига и другим входом генератора и является входом устройства, причем выход дешифраторя подключен к второму входу второго анализатора, огэгичагощее(. г тем, что, с целью повышения помехоустойчивости и сокращения времени вхождения в синхронизм, введен дополнительный накопитель, вход которого соединен с выходом делителя, а выход — с трстьиы Входом блока сОВпадения.

Источники информации, принятые во внимание при экспертизе:

I. Левин Л. С. и Плоткин M. Л.)Ос(!013ы построения цифровых систем передачи. М., «(.Вязь)>, 1975, c. !6 — 120.

623260

Составитель Т. Маркина

l сдактор Г. Марковская Тскрсд О. Луговая Корректор Е. Г!апп

:Заказ 4029/49 Тирани 805 Подписное

LIHI4IiI1H Государственно о комитета Совета Министров СССР по делам нзОбретений и открытий 30;35, Москва, Ж-35. Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, >л. Проектная, 4