Ячейка памяти для матричной однородной структуры

Иллюстрации

Показать всеРеферат

Сова Советских

Соцналистмцесккх

Республик

QllИСAНИЕ

ИЗОБРЕТЕН ИЯ

К А8ТОРСКОМУ СВИДЮТВЛЬСТВУ (11) 624295 (6l) Дополнительное к авт. свнд-ву(22) Заявлено 17.08.76 (21) 2398612/18-24 с присоединением заявки №(23) Приоритет—

3 (51} М. KJAlx б 11 С 11/40

Я 06 F 7/00

Государственный квинтет

Совета Министров СССР

R0 делам изобретений н открытий (43) Опубликовано15.09.78.Бюллетень № 34 ъ (45) Дата опубликования описания 04.08.78 (53) УДК 681.327 (088.8) В. Ф. Гусев, Г. H. Иванов, В. Я. Контарев, Г. И. Кренгель, B. Я. Кремлев, М. 3. Шагивалеев, Ю. И. Шетинин и А. У. Ярмухаметов (72) Авторы изобретения

)r IQ

y g in) !1б (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ МАТРИЧНОЙ ОДНОРОДНОЙ

СТРУКТУРЫ

Изобретение относится к области ав- томатики и вычислительной техники и предназначено для использования в качестве функционального элемента универсальных и специализированных однород ных структур (вычислительных сред).

Известны ячейки памяти для матричной однородной структуры, содержащие триггер, информационные и адресные шины, дополнительный настраиваемый эле- 10 мент.

Информационные шины используются в режиме настройки t1)

Недостатки известных ячеек памятиневозможность работы по нескольким на- 15 правлениям с одной магистралью и ограниченные функциональные возможности, обусловленные организацией выхода ячейки.

Из известных наиболее близким техническим решением является ячейка памяти, содержащая Ll- триггер выход которого подключен к первым вхбдам элементов И-НЕ, вторые входы которых подключены к адресным шинам считывания, а выходы элементов И-HE подключены к соответствуюшим информационным входам Д-триггера ..(2)

СЬнако эта ячейка памяти имеет низкие эксплуатационные характеристики при объединении ячеек в матрицы боль шого объема, что необходимо при построении устройств для обработки данных типа вычислительных машин.

Цель изобретения - улучшение эксплу-, атационных, характеристик путем обеспечения возможности автономного управле ния при объединении ячеек в матричную однородную структуру.

Зга цель достигается введением в предлагаемую ячейку памяти элементов

HE (компенсирующих инверторов), входы которых подключены к адресным шинам записи, а выходы - к соответствующим информационным входам Д.григгера.

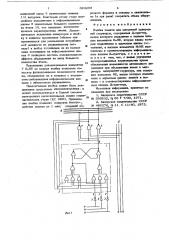

На фиг. 1 изображена ячейка. памяти для матричной однородной структуры; на фиг. 2 - объединение ячеек в матрицу.

Д триггер 1, выделенный на фиг. 1 пунктиром, подключен адресными вхо624295 дами 2 записи к элементам 3 HE (компенсирукнцим инверторам), входы которых соединены с адресными шинами; 4 записи. gpyrHe входы 5 й-триггере 1 подключены к информационным шинам 6

5 и к выходам элементов 7. И-НЕ, пер вые входы которых подключены к выходу 8 Д-триггера 1, а другие их входы подключены к адресным шинам 9 считывания, Ячейка работает следуюшим образом.

Запись информации в ячейку осуществляется с информационных шин 6 путем пОдачи сигналОВ записи HB адресные шины

4 записи. Сигналы записи с соответствующей из адресных шин 4 через элементы

3 НБ разрешают прием не Д григгер 1 информации с соответствующей из информационных шин 6,, Зля считывания информации из ячейки на. одну из информационных шин 6 достаточно подать по адресным шинам 9 считывания сигнал на вход соответствующего элемента 7 И-НЕ. При этом на информационной шине 6, подключенной к выходу элемента 7 И-НЕ, будет потенциал, соответству.мций содержимому И григгере 1, записанному предварительно с той же информационной шины 6 или с любой друГой из инфОрмациОнных шин 6, Ячейки 10 матричной однородной структуры объединяются в матрицы (см. фиг.2), Одноименные выходы ячеек 10 объединяются между собой с помощью информационных шин 6, с которых возможна кек

35 .запись в ячейки 10, так и считывание иэ ячеек 10 на информационные шины 6, Адресные входы ячеек 10 объединяются с помощью адресных шин 4 записи и вдресных шин 9 считывания соответст4О венно . Обработка информации в матрице производится в процессе передачи инфор.мации по информационным шинам 6 от ячейки к ячейке или при одновременной работе нескольких ячеек 10. Например, 45 логическая операция И осуществляется

Одновременным считыванием .НВ сООТВетствуищую информационную шину 8 содержимого сразу двух ячеек 10. При этом единичная информация на информационных шинах 6 остается только в тех разрядах

56 матрицы, ие которые одновременно считыВались единицы, 8 разрядax жег на которые считывался хотя бы один "нуль! „ остается",нулевая информация.

Операция ИЛИ выполняется одновре55 менной записью в одну ячейку 10 информации с различных информационных шин

6. При этом, если хотя бы одна "единое BGTb HB любой HG информационных шин 6, она записывается в данную ячейку 10.

Операции перекомпоновки выполняются не ячейках 10, различные выходы которых эекоммутированы с информационными шинами 6 других столбцов матрицы (на фиг. 2 см. нижнюю строку матрицы). Например, операции сдвигов вправо выполняются записью в эту строку по первым входам ячеек с пургой информационной шины 6, е чтением - по второму выходу не другую информационную шину 6 сдвиг влево - в обратном порядке. Операции пересылок информации выполняются путем считывания содержимого одной ячейки 10 и зелиси вдругую,,причем передающая ячейка 10 является источником, е все прочие не этой информационной шине 6 - приемниками, Одновременно возможна пересылка информации между другими ячейками; 10 по другой ииформаI ционной шине 6; между третьей группой ячеек (в которую частично могут входить и уже работающие по другим шинам ячейки) производится пересылке по третьей шине 6 и т.д..

Для получения сети "каждый с каждым необходимо иметь столько входов и выходов у ячейки, сколько пересылок может существовать одновременно. Экспериментально доказано, что для построения процессора ЭВМ необходимо и достаточно иметь ячейку с тремя выходами.

При этом по одной шине пересылается первый операнд, по другой шине- второй операнд, е по третьей - -результат обработки, Однако количество ячеек, подключенных к шинам, ограничено, Выходные элементы 7 И-НЕ имеют ограниченную негруэочную способность, причем не очень большую. Мощные элементы не выходе приводят к значительному ухудшению параметров выходного сигнала. Обычно принято, что элементы могут быть нагружены на 10 подобных элементов. И хотя в матрице все подключенные ячейки 10 не могут одновременно быть потребителями тем не менее каждый вход й-триггере 1 потребяет 1/2 нагрузки. Для, устранения этого недостатка введены, дополнительные элементы

3 HE (компенсирующие инверторы). Пара« метры. этих.инверторов подобраны так, что потенциал не их выходе в закрытом состоянии, т.е. когда нет записи в данную ячейку 10, значительно ниже потенциале на информационной шине 6 и, значит не другом входе Дгриггере 1. Происходит перераспределение токов таким обрезом, что потребление тока с инфор624295 мационной шины 6 значительно меньше

1/2 нагрузки. Благодрая этому стало возможным подклкиение к информационным шинам 6 значительно большего .количества ячеек 10, что повышает эксплуатационные характеристики; ячеек.. Допол- . нительное включение инверторов в ячейку в неявном применении (обычно они применяются для уменьшения потребляемой мошности по управляюшему сигналу) и выбор потенциала на их выходе

10 ниже потенциале на информационных шинах 6 позволило достичь положительного эффекта объединения на шину большого количества ячеек.

Применение дополнительных элементов

1$

7 И-НЕ на выходе ячейки позволило повысить функциональные возможности ячейки, объединение их s матрицы с незави симо работающими информационными шн20 нами с автономным управлением.

Предлагаемая ячейка может быть реализована. средствами микроэлектроники; и может использоваться в Единой системе электронных. вычислительных машин социалистических стран (ЕС. ЭВМ). Примене2$ ние ячейки позволит повысить быстро- действе модели до 1 млн, операций короткого формата в секунду и эначитель но (в три раза) сократить обьем обору дования.

Формула изобретений

Ячейка памяти для матричной однород ной структуры, содержашая @триггер, выход которого подклеен к первым вхо дам элементов И-НЕ, вторые входы которых подключены к адресным шинам счи=тывания, а выходы элементов И НЕ подключены к соответствующим. информациокным входам @триггера, о т л и ч а ю ш а я с я тем, что, с иелмо улучшения эксплуатационных характеристик путем обеспечения воэможности автономного управления прн обьединеиии ячеек в матричную однороднуюструктуру, она содержит элементы НЕ, входы KoTopblx подкл20 чены к адресным шинам записи а выходы - к соответствуюшим информациоцным входам Д-триггера.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

М 395832, (j 06 Р 7/00, 1971.

2. Авторское свидетельство СССР

% 486376, Я 11„С 11/40, 1973.

624295

Составитель P. Яворовская

Редактор Л. Жаворонкова Техред К. вврон Корректор E. Папп

Заказ 5196/43 Тираж 717 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушскаа иаб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,