Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ФСеюе1има 0 д

О П И ."А -Н И" Е

ИЗОБРЕТЕНИЯ

Союэ Советских

Социалистических

Ресяу блик (11) 625248

К АВТОРСКОМУ СВИДЙТИЙЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено 28.03.77(21) 2471420/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано25.09.78.бюллетень № 35 (45) Дата опубликования описания 22,0аЛ8 (51) М. Кл.

Q 11 С 17/00

Государственный квинтет

Совета Мнннстраа СССР пе делан нэееретений и открытей (@3 У Ж 628.327.

° 6 (088.8) (723 Ь.вторы изобретения

К. Г. Вълков,, В. И. Корнейчук, В. П. Тарасенко и А. В. Городний

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (71) Заявитель (54) постоянною злломинлющяя уст1 ойство

Изобретение относится к вычислительной технике и может быть использовано в цифровьос вычислительных машинах.

Известны постоянные запоминающие устройства для .хранения значений логичес- н ких функций, однако, эти устройства мало эффективны в отношении емкости памяти при реализации логических функций над многоразрядными операндами (1).

Наиболее близким техническим решением к изобретению является постоянное запоминающее устройство для хранения логических функций, содержащее регистр кода функции, соединенный через дешифратор с накопителем, регистры операндов и регистр результата (21. Это устройство имеет низкую надежность.

Белью изобретения является повышение надежности устройства.

Достигается это тем, что устройство 2О содержит дополнительные дешифраторы и элементы И-ИЛИ, входы которых подключены к выходам накопителя и соответствующим выходам дополнительных дешифраторов, а выходы элементов И-ИЛИ соеди- 25 нены с входами регистра результата, входы дополнительных дешифраторов соединены с соответствующими выходами регистров операндов.

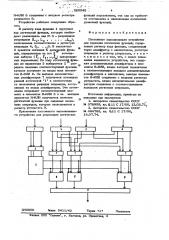

На чертеже представлена функциональная блок-схема постоянного запоминающего устройства.

Устройство содержит регистр кода функции 1, дешифратор адреса 2 и накопитель

3, регистры операндов 4, 5, ... >6, дополнительные дешифраторы 7 и элементы

И-ИЛИ 8 и регистр результата 9. Выходы регистра кода функции 1 через дешифратор адреса 2 подключены к входам накопителя 3. Выходы старших (n -ых) разрядов регистров операндов 4, 5 ..., 6 подключены к входам дополнительных дешифраторов 7, выходы (" — 21)-ых разрядов регистров операндов 4, 5>...т6 подключены к входам следующего дополEHTQJIhHoI дешифратора, Выходы каждого дополнительного дешифратора подсоединены к первым входам элемента И-ИЛИ 8, к вторым входам которого подключены выходы накопителя 3. Выходы элементов функций перспективно, так как не требуется составление, и минимизация логических уравнений функций, Постоянное запоминающее устройство для хранения логических функций, содержащее регистр кода функции, соединенный через дешифратор с накопителем, регистры операндов и регистр результата, о т л и— ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит дополнительные дешифраторы .и элементы И-ИЛИ, входы которых подключены к соответствующим выходам дополнительных двшифраторов и накопителя, выходы элементов И-ИЛИ соещинены с входами регистра результата, входы дополнительных дешифраторов соединены с соответствующими выходами регистров операндов.

Источники информации, принятыв во внимание при экспертизе:

1. Авторское свидетельство СССР

% 378959, кл. 6 11 С 17/00, 12.03.71е

2. Авторское свидетельство СССР

Ж 494768, кл. < 11 С 17/00р

1 8.07. 74. у 4

; ° Ð а.

« „Г . м д

3, 635248 4

И-ИЛИ 8 соединены с входами регистра результата О.

Устройство работает следующим образом.

В регистр кода функции 1 поступает код логической функции, которую необхо5

Формула изобретения димо реализовать над П1 Il - разрядными операндами (1.; g „L ° ° ° ° - -. L ) в записанными соответственно в регистрах операндов 4 5 . ... 6. В накопителе

3 хранятся значения К логическях функ ций, опрвделенныв на все Я возможных наборов (8, . Ц одноразрядных переменных. По коду логической фуикm цин из накопителя 3 выбирается 2 разрядное значение соответствующей функции, котооое поступает на аходы всех элемен« тов И-ИЛИ 8. На выходах дополнительных дешифраторов 7 получается потенциал равный логической 1 в соответствии

20 со значениями разрядов операндов, поступивших на входы дешнфраторов. Эти потенциапы открывают соответствующий weмент в элементах И-ИЛИ 8 .и на выходах элементов И-ИЛИ получаются значения логической функции при заданных значениях операндов, которые записываются в регистр: результата 9.

Применение постоянного запоминающе.го устройства для реализации логических цниипи Заказ 5411/42 Тираж,717

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Подписное