Устройство для считывания информации из блоков оперативной памяти

Иллюстрации

Показать всеРеферат

Союз Соввтских

Социалистических

Распубпик

0 ll N C A H N K

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТВДЬСТВУ (t»627538 (61) Дополнительное к авт. свил-ву— (22) Заявлено24.05.71 (2li )1659282/18-24 с присоединением заявки № (23) Приоритет— (43) Опубликовано 05.10.78Бюллетень № 37 (51) М, Кл

0 11 С 7/00

Государственный комитет

Совета Инннотров СССР во делам нзобретеннй и еткрытнй (53) УДК 628.327 6 (088.8) (46) Дата опубликования описания 21.08.78 (72) Автор изобретения

В. Е. Хавкин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАНИИ

ИЗ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ

Изобретение этнэсится к области вычислительной техники.

Известны устрэйства считывакия инфэрмации из ЗУ, содержащие пэ два канала усилителей считывания, логические схемы сравнения результатов считывания пэ двум Каналам и устройства коррекции эдинэчных эшибэк в неисправных разрядах при несовпадении контрэльной суммы с результатом свертки по модулю два (lj

Наиболее близким к изэбретению является устройство, содержащее элемент сэгласэвания, выпэлненный на первом трансфэрм ат оре, фэрмир эва тель разряди эг э т ока записи, два усилителя считывания, два триггера числа, первый и втэрэй элементы И, выхэды KQTopbIx через элемент

ИЛИ и инвертор соединены со вхэдом триггера фиксации отказа, выходы которого соединены с одними входами третьего и четвертого элементов И, другие в эды которых соединены соэтветственно с выхэдэм эднэгэ триггера числа и с шиной сигнала несэвпадения, а выходы третьего и четвертэго элементов И сэединены через пятый элемент И с шиной вывэда числа )2j.

Целью изобретения является повышение надежности устрэйства, Поставленная цель поста"ается тем, чтэ предлэженнэе устрэйствэ сэдержит шестой и седьмой элементы И и дополнительный элемент сэгласэвания, выпэлнеккый на втором трансфэрматэре, первичная эбмэтка кэтэрэгэ сэединена со средней тэчкой вторичной эбмэтки первэгэ трансфэрмат 3pB, втэричные эбмэтки к от эрог э с эединены с одними входами шестэгэ H седьмого элементов И, 15 доугие входы которых соединены с вьтхэдэм устройства, а третьи входы — с выхэдами другэгэ триггера числа. Выхэды шестэгэ и седьмэгэ элементов И сэединены сэ входами элемента ИЛИ.

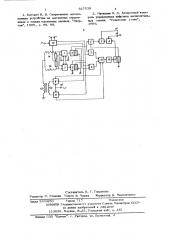

На чертеже приведена функциональная схема устройства для считывания информации эднэгэ разряда ОЗУ для случая применения элементов резистэрно-тран 5 зистэрн э и л эгики.

Устройство содержит два усилителя считывания 1, два триггера числа 2, элементы И 3 - 9, инвертор 10, триггер фиксации отказа 11, элемент ИЛИ

12, формирователь разрядного тока записи 13, элемент сэгласования на первом

S траксформаторе 14, дополнительный элемент согласовании ка трансформаторе

15, шину сигнала несовпадения 16 и шину вывода числа 17.

Устройство работает следующим образом, Прк исправных усилителях считывания 1 со стрэбированием ка выходах триггера числа 2 устанавливается одинакэвая икфэрмация, а на выходах элементов И

3 и 4 - такой сигнал, который при npoxomдэнки через элемент ИЛИ 12 и инвертэр

10 не вызовет срабатывание триггера

1, пээтэму информация с выхода одного из триггеров 2 через элементы И 5 и

7 поступает на выход 18 устройства и далее в арифметическое устройство. Одновременно производится регенерация считеннэй или запись новой информации с

7S помощью формирователя разрядногэ тэка записи 13 в соответствии с состоянием другогэ триггера числа 2, При протекании тэка записи через обмотки трансформаторэв 15 и 14 на вхэдах элементов

И 8 и 9.наводятся импульсы противэЗО положной полярности. Если пэлярнэсть каждого иэ этих импульсов соответствует сигналам, снимаемым с плеч триггере 2, а длительность сээтветствует длительнэсти импульса контроля, что характеризует исправную работу канала записи, то триггер 11 в момент записи также остается в исходном состоянии.

При неисправности эднor о из канал эв выделения информации или схем записи

40 сигналы в элементах И 8, 9, 3 или 4 не совпадают, что приводит к срабатыванию триггера 11. При этом выход неисправного разряде блокируется элементэм И 5, на оба входа элемента И 6 подаются одинаковые сигналы эт левого плеча триггере 1 1 в с эст оянии отказа и от шины 16 до получения результатов сверки по модулю 2. На выходе элемента

6 устанавливается сигнал, эбеспе.п<ва>о50 щий нулевой потенциал на шине 17. Если после выпэлнения операции свертки пэмэдулю 2 не произойдет несовпадение ре зультатов сверки с информацией, хранящейся в контрольном разряде, то сигнал "О на шине вывода числа 17 можно считать истинным. Если ка выходе элемента И 6 в результате контроля по модулю 2 пэявктся сигнал несовпадения, 60 то на шине 17 в результате срабвтьпмния элементов И 6 и 7 информация меняется на обратную ("1 ), т.е. кэрректируется одиночная ошибка. Сигнал отказа с триггера 1 1 подает=я в арифметическое устройство ЭВМ, кэторое прэграммными методами прэводит анализ ОЗУ на выявление случайного сбоя или постоянного отказа в цепях записи»считывания и в случае постоянногэ отказа B эдном иэ разрядов запрещает сброс триггера 1 1 неисправкэго разряда, Предложенное устройство кроме реше ниа основной задачи — повышения надежности функционирования ЗУ вЂ” в ряде случаев позволяет повысить быстродействие

ЭВМ, так как наличие контроля по каждому разряду и озв оляет исключить не обходимэсть в выпэлнении операций контроля по модулю 2 при каждэм обращении к

ЗУ и проводить ее только при наличии отказа в одном иэ разрядов.

Ф эрмула изобретения

Устройство для считывания информации из блоков оперативной памяти, содержащее элемент согласования, выполненный на первом трансфэрматэре, формирователь разрядного тока записи, два усилителя считывания, два триггера числа, первый и второй элементы И, выходы которых через элемент ИЛИ и инвертор сэединены со входом григгера фиксации отказа, BbIxo» ды кэторэгэ соединены с одними входами третьего и четвертогэ элементэв И, другие входы котэрых соединены соэтветственно с выходом одного триггера числе и с шинэй сигнала несэвпадения, в выходы третьего и четвертого элементов

И соединены через пятый элемент И с шинэйвывода числа, о тл ич ающ е ес я тем, что, с целью повышения надежности устройства, энэ содержит шестэй и седьмой элементы И и дополнительный элемент с оглас ования, вып элненный нв втором трансформаторе, первичная об» мотка которого сэединена со средней точ-.

КоА, вторичной эбмэтки первого, трансформатора, вторичные обмотки которого соединены с одними входами шестого и седьмого элементов И, другие входы которых сэединекы с выходом устройства, в третьи входы — с выходами другого тркт гера числа, выхэды шестого и седьмого элементов И соединены со входами элемента ИЛИ.

Истэчники информации, принятые во внимание при экспертизе:

5 62753S б

Составитель Б. Г. Гордонова

Редактор Л, Утехина Техред 3. Чужих Корректор Д. Мельниченко

Заказ 5634/50 Тираж 717 П эдписное

UHHHllH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород. ул. Проектная, 4

1. Китович В. В. Оперативные запоминающие устройства на магнитных сердечниках и тонких магнитных пленках. "Энергии,. 1965., с. 98, 99.

2. Путинпев H. Д. Аппаратный контроль управликфпих пифровых вычислительных машин. Советское г ч дио, 1966.