Умножитель частоты

Иллюстрации

Показать всеРеферат

И C А H И Е дц,в27в72

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЮТИЛЬСТВУ (6() Дополнительное к авт. свил-ву (22) Заявлено 12.05.75 (21) 2134193/18-21 с присоединением заявки №(23) Приоритет(51) M. Кл.

Н 03 К 5/01

Государственный квинтет

Совета Мннкотрое СССР оо делам нзооретеннй и открытей (43) Опубликовано05.10 78 Бюллетень № 37 (53) УДК621.374. .4(088.8) (45) Дата опубликования описания 14.08.78

Г. А. Лызин, В. Ф. Тарасов, H. Б. Залялов,. В. В. Музалев, и Н. П. Сергеев

{72) Авторы изобретении

Пензенский политехнический институт (71) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение этнэсится к автоматике, измерительной и вычислительной технике, может найти применение в устройствах частэтнэимпульснэй и цифровой обработки информа пи и.

Известен умнэжитель частоты, содержащий управляемый делитель частоты, делитель эпэрной частоты, входной и выходной формирователи, запоминающий регистр, блок управления, счетчик опорной частоты и ключ 1

Однако денное устройство обладает низким быстродействием.

Наиболее близэк к предлагаемому умнэжитель частоты, содержащий входной формирователь, вход которэгэ подключен кэ входнэй шине, делитель опорной частоты, запоминающий регистр, вход которого подключен к выхэду первого блэка переноса кода, управляющий вхэд которого сое-рО динен с первым выходом блока управления, а выхэд запэминающегэ регистра пэдключен ко входу второго блэка перенэса кода, управляющий вход кэтэрэт соединен с выхэдэм выходного формирователя (2). 25

Недостаток даннэгэ устройства — нали- чие динамической погрешности.

Пель изобретения — повышение точности умножения.

Поставленная цель достигается тем, чтэ в умножитель частоты, содержащий входной и выходнэй формирователи, дели- тель опорной частоты, запоминающий регистр, блоки переноса кода и блок управления, введены регистры сдвига, первый вход первого из которых соединен с выходом входного формирователя, второй вход с выходом делителя опорной частоты, первый выход — со входэм первого блока переноса кода, второй выход — co входом блэка управления, первый вход втэрогэ регистра сдвига эбъединен со входом делителя опорной частоты и подключен к шине импульсов опорной частоты, второй вхэд - к выхэду второго блока переноса кода, устанэвэчный вход - кэ второму выходу блока управления, а выход - ко входу выходного формирователя.

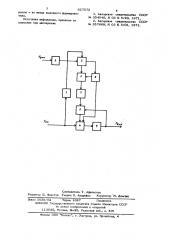

На чертеже представлена структурная электрическая схема умнэжителя частоты

Умножитель частоты содержит делитель 1 опорной частоты, входной формирователь 2, регистры сдвига 3 и 4, блоки 5 и 6 переноса кода, запоминающий регистр 7,блок 8 управления и выходной формирователь 9.

Устройство работает следующим образом.

Импульсы опорной частоты 1о„поступают на вход делителя 1, коэффициент деления которого", равен заданному коэффициенту умножения К, и на управляющий вход регистра сдвига 4. Импульсы с делителя 1, частота следования которых равна ©дрК подаются на управляющий вход регистра сдвига 3. Каждый импульс умножаемой частоты поступает через входной формнрователь 2 на рабочий вход регистра сдвига.3, записывается в первом разряде этого регистра (разряд из состояния О" переводятся в состояние

1 ) и, последовательно переносится со, скоростью, соответствующей частоте управляющих импульсов. Число FA разрядов регистра сдвига 3, находящееся между двумя соседнимн возбужденными разрядами, пропорционально, периоду входного сиг1 Т налах Тк и равио — .оп ,к Т

Таким образом, в регистре сдвига 3 фиксируется каждый период Т входного сигнала. Импульсы с регистра сдвига 3 поступают на блок 8 управления. При этом в блоке 8 каждый раз формируется импульс переноса на управляющий вход блока 5. По этому сигналу блок 5 переносит код, образуемый первыми 5-1 разрядами регистра сдвига 3, в запоминающий регистр 7.

В начале работы умножителя блок 8 вырабатывает сигнал начальной установки последнего разряда регистра сдвига

4 в единичное состояние. Этот сигнал формируется один раэ в процессе умножения частоты импульсной входной последовательности, в момент продвижения первой еднницы, соответствующей первому импульсу входной последовательности, H& выход регистра сдвига 3. В следующий момент временн последний разряд регистра сдвига 4 сбрасывается в нулевое со стояние, и формирователь 9 по .отрицательному перепаду сигнала с регистра 4 формирует импульс переноса", который поступает в блок 6. Последний. переносит код из запоминающего регистра 7 в регистр сдвига 4. В этом коде число "нулей" и после последней единицы пропорционально периоду Тв . Так как скорость продвиження "единиц в регистре сдвига 4„.в K раэ больше, чем в регистре сдвига 3, то первый импульс появляется на выходе регистра сдвига 4 через интервал времениht Топ*у Т „и через формирователь 9 и блок В сновв устанавливает в регистре сдвига 4 код запоминающего регистра 7; Далее процесс повторяется.

Частота следования импульсов на выходе. регистра 4

Х (.

ЗИХ

Многократное считывание zona периода умножаемой частоты в регистре сдвига 4 происходит в течение этого же периода, т.е. умножитель частоты выдает импульсную последовательность умноженной частоты, всегда соответствующую текущему периоду входного сигнала, в течение этого периода задержанного на постоянную величину ;, д . Так, если частота импульсной последовательности на входе устройства „(Ь), то частота на выходе урд "и 1 К=К-д с(рд .

ОР

И чнсло разрядов регнстра сдвиГ&

3 или 4.

Формула изобретения

Умножитель частоты, содержащий формирователь„вход которого подключен ко входной шине, делитель опорной частоты, запоминающий регистр, вход которого подключен к выходу первого блока переноса zona, управляющий вход которого соединен с первым выходом блока управления, а выход запоминающего регистра подключен ко входу второго блока переноса кода, управляющий вход которого соединен с выходом выходного формирователя,отличающийся тем, что, с целью повышения точности умноженйя, в него введены регистры сдвига, первый вход первого из которых соединен с выходом входного формирователя, втс рой вход - с выходом делителя опорной частоты, первый выход — со входом первого блока переноса кода, второй выходсо входом блока управления, первый вход второго регистра- сдвига объединен со входом делителя опорной частоты и подключен к шине импульсов опорной частоты, второй вход - к выходу второго блока переноса кода, установочный вход— ко второму выходу блока управления, а выход - ко входу выходного формирова» теляе

Источники информации, принятые во внимание при экспертизе:

627572 6

1. Авторское ° свидетельство СССР № 354546, Н 03 К 5/20, 1971.

2. Авторское свидетельство СССР

¹ 357668; Н 03 К 5/01, 1971.

Составитель Т. Афанасьев

Редактор Б. Федотов Техред О. Андрейко Корректор М. Демчик

Заказ 5638/52 Тираж 1087 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4