Логический элемент

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

О П И С А Н И-Е

ИЗОБРЕТЕНИЯ

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-By— (22) Заявлено 06.05.77 (21) 2482821/18-21 с присоединением эаявки №вЂ” (23) Приоритет— (43) ОпублИковано 051078 Бюллетень № 37 (51) М. Кл.

Н 03 К 19/08

Государственннй комитет

Совета Министров СССР по делам изобретений и открытий (gg) УДК 621.374 (088.8) (45) Дата опубликования описания 15.0878 (72) Автор изобретения

А.Н.Кармаэинский

Московский ордена Трудового Красного Знамени инженерно-физический институт (71) Заявитель (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к области вычислительной техники, электроники, автоматики и, в частности, может быть использовано при разработке больших интегральных схем на дополняющих МДП-транзисторах.

Известны инверторы на дополняющих

МДП-транзисторах и логические элементы, выполняющие различные логичес-. кие функции, существенными признаками которых является наличие пар дополняющих транзисторов, П- и р-канальных, в которых сток и-канального транзистора подключен к стоку рканального транзистора и к логическому выходу элемента, затвор и -канального транзистора подключен к затвору р-канального транзистора и к логическому входу элемента, истоки П-канальных транзисторов и их подложки подключены к общей шине, истоки р-кайальных транзисторов и их подложки подключены к плюсовой шине (1) .

Недостатком известных логических элементов является наличие, только одного выхода.

Известен логический элемент, содержащий ряд инверторов на дополняющих МДП-транзисторах, первый инвертор подключен между шинами источника питания, а следующий — между одной иэ шин источника питания и выходом предыдущего инвертора, причем вход и выход каждого из инверторов являются соответственно входом и выходом элемента, в каждом из инверторов подложки н -канальных транзисторов подключены к общей шине, а подложки р-канальных транзисторов — к плюсовой шине j27.

Недостатком известного элемента является то, что на выходе каждого инвертора Реализуется только функция НЕ-И (либо тЙЕ-ИЛИ ) для входных, сигналов этого инвертора и всех предшествующих. цель изобретения — Расширение функциональных возможностей элемента.

Для достижения поставленной цели в логическом элементе, Содержащем три инвертора на дополняющих МЛПтранзисторах, в котором первый инвертор подключен между шинами источника питания,,второй — между выходом первого и одной из шин источника питания,,вход и выход каждого из инверторов являются соответственно входом и выходом элемента, и в каж.дом из инверторов подложки й-каналь627593 ных транзисторов подключены к общей шине, а подложки р-канальных транзисторов — к плюсовой шине, третий инвертор включен между выходом первого инвертора и одной из шин источника питания, не подключенной ко второму инвертору, вход третьего инвертора подключен ко входу второго инвертора.

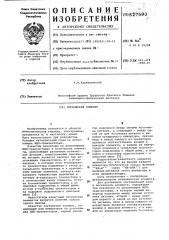

На фиг. 1 представлена принципиальная схема элемента, где первый инвертор 1 на дополняющих МДП-транзисторах 2 и 3 включен между плюсовой шиной 4 и общей шиной 5, второй ин- вертор 6 на дополняющих МДП-транзисторах 7 и 8 включен между общей шиной 5 и выходом 9 первого инвертора

1, а третий инвертор 10 на дополняющих МПП-транзисторах 11 и 12 включен между плюсовой шиной 4 и выходом 9 первого инвертора;1. Вход 13 первого инвертора 1 и вход 14 второго инвертора 6, объединенный со входом третьего инвертора 10, являются, соответственно, входами элемента.

Выход 9 первого инвертора 1, выход

15 второго инвертора 6 и выход 16 третьего инвертора 10 являются, соответственно, выходами элемента.

Подложки и -канальных транзисторов 2, 7, 11 подключены к общей шине 5, подлои<и р-канальных транзисторов

3, 8, 12 — к плюсовой шине 4.

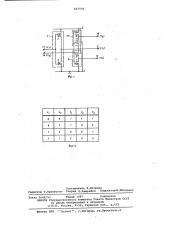

На фиг. 2 представлена таблица истинности, поясняющая работу элемента.

Элемент работает следующим обра- ° зом. Если на входы 13 и 14 поступает напряжение логического нуля, то закрыты д-канальные транзисторы 2, 7, 11, а р-канальные транзисторы

3, 8, 12 открыты.

Следовательно на всех выходах 9, 15, 16 устанавливается напряжение. логической единицы. Если на вход 13 поступает напряжение логического нуля, а на вход 14 — напряжение логической единицы, то транзисторы 8 и

12 закрываются, а транзисторы 7 и

11 открываются. Так как открыт транзистор 3, то на выходе 9 напряжение соответствует напряжению логической единицы и через транзистор 11 это напряжение передается на выход 16.

Отпирание транзистора 7 приводит к тому, что на выходе 15 устанавливается напряжение логического нуля.

Если на входе 13 — напряжениЕ логической единицы, а на входе 14— напряжение логического нуля, то открыты транзисторЫ 2, 8, 12, а закрыты транзисторы 3, 7, 11. Через открытый р-канальный транзистор 12 на выходе 16 устанавливается напряжение логической единицы, а на выходах 9 и 15 через открытые транзисторы 2 и

8 — напряжение логического нуля. При напряжении логической единицы на обоих входах 13 и 14 открываются транзисторы 2, 7, 11 и закрываются

10 транзисторы 3, 8, 12, при этом на всех выходах устанавливается напряжение логического нуля.

Таким образом, в соответствии с таблицей истинности, на выходе 9 (У ) выполняется Функция "НЕ от входной переменной Х„ на входе 13, на выходе 15 (у ) — Функция ИЛИНЕ, а на выходе 16 (У ) — функция И-НЕ от двух входных переменных

Х, и Х, на входах 13 и 14.

Таким образом, на каждом из выхо" дов данного элемента формируются различные функции от входных переменных, что расширяет Функциональные возможности элемента при использовании его в аппаратуре °

Формула изобретения

55 е

Логический элемент, соцержащий три инвертора на дополняющих МДПтранзисторах, первый инвертор под" ключен между шинами источника питания, второй — между выходом первого инвертора и одной иэ шин источника питания, вход и выход каждого из инверторов являются, соответственно, входом и выходом элемента, в каждом из инверторов подложки ll-канальных транзисторов подключены к общей шине, а подложки р-канальных транзисторов — к плюсовой шине, о т л и ч а ю шийся тем, что, с целью расширения функциональных возможностей, третий инвертор включен между выходом первого инвертора и одной из шин источника питания, не подключенной ко второму инвертору, вход третьего инвертора подключен ко входу второго инвертора.

Источники информации, принятые во вниманИй при экспертизе:

1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М., Сов. радио, 1973.

2. Патент Великобритании 91300495, кл. Н 3 Т, 1972.

627593

4 иг. t

Фиг,2

Составитель Л.Петрова

Редактор Т, Орловская Техред O. Aидрейко Корректор A Власенко

Заказ 5640/53 Тираж 1087 Подписное

ЦИИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раумская наб., д.4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4