Устройство для возведения двоичных чисел в квадрат

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное к авт. свил-ву— (22) Заявлено 07.03.75 (21) 2111763/18-24 с присоединением заявки № (23) Приоритет(43) Опубликовано15.10.78.Бюллетень №38

{46) Дата опубликования описания28.08.78

< " 628487

Союз Советских

Социалистических

Республик

".:5 П Т Б

1 --... „-..«.г(-.

2 (51) М. Кл.

Я 06 1 - 7/Э8

Государственный иовитет

Совета Министроа СССР по делам изооретений и открытий (5Ч ЬЧК В81.зг5 (088.8) (72) Авторы изобретения

В. М. Ерухимович, Н. С. Преображенский и В. Г. Казаков (71) Заявитель (54) УСТРОЙСТВО LlJIH ВОЗВЕДЕНИЯ ДВОИЧНЫХ

ЧИСЕЛ В KBAQPAT

Изобретение относится к области вычислительной техники и может быть ис пользовано в стохастических вычислитель ных машинах для возведения в К ю степень чисел, представленных в двоичной форме.

Известно множительное устройство, содержащее регистры числа, логические элементы, рабо тающие по вероятностно-импульсному принпипу (lj . Опнако YoIBQGTh О этого устройства ограничена.

Наиболее близким техническим решением к данному изобретению является уст ройсгво для возведения двоичных чисел в квадрат, содержащее счетчик, счетный т5 вход ко срого через элемент И соединен с выходами блока элементов ИЛИ, первая и вторая группы входов которого соединены с выходами первого и второго коммутаторов соответственно, первые группы 20 входов которых соединены с выходами регисара числа соосаасссааннс (2j

B этом устройстве двоичное число преобразуется в К случайных последовательностей с вероятностями появЛения импульса, пропорциональными исходному числу. Указанный метод кодирования позволяет применить К-входовый элемент И для возведения двоичного числа е К-ю степень, что существенно упрощает схему множительного устройства. Однако при представлении двоичного числа случайны ми последовательностями го ность вычислений находится в зависимости or длины декодируемой с помощью счетчика последовательности, представляющей результат вычислений. Поэтому достижение высокой точности вычислений приводит к значительному снижению быстродействия устройства.

Целью изобретения является повышение быстродействия устройства.

Для достижения поставленной цели предлагаемое устройство содержит рекуррентный регистр сдвига, блок сумматоров по модулю два, первый и второй блоки элементов И, выходы которых подключ ны ко вторым группам входов первого и второго коммутаторов соответственно, входы первого блока элементов И подклю3

628487 чены к первой группе выходов рекуррентного регистра сдвига соответственно, Вторая группа выходов которого соединена со входами блока сумматоров по модулю

gaa соответственно, выходы которого соединены со входами второго блока элементов И соответственно, управляющий вход. счетчика соединен„ с последним выходом первого блока элементов И.

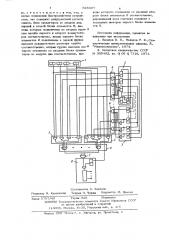

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит регистр 1 числа, рекуррентный регистр сдвига 2, блок сумматоров по модулю gaa 3, первый и второй блоки элементов И 4, первый и второй коммутаторы 5, блок элементов NEIN

6, элемент И 7 и счетчик 8.

Рекуррентный регистр сдвига 2, выходы разрядов которого подключены ко входам первого блока элементов И 4, первый коммутатор 5, первые входы которого цри- 20 соединены к выходам разрядов регистра 1, а вторые — к выходам первого блока элементов И 4, и блок элементов ИЛИ 6, входы которого подключены к выходам коммутатора 5, составляют преобразователь двоичного числа в псевдослучайную импульсную последовательность.

Блок сумматоров по модулю два 3, вхо-. ды которого подключены к выходам разрядов регистра 2, а выходы — ко входам второго блока элементов И 4, второй коммутатор 5, первые входы которого присоединены к выходам разрядов регистра 1, а вторые — к выходам второго блока элементов И 4 и блок элементов ИЛИ 6, вхо- ды которых подключены к выходам коммутаторов 5, составляют преобразователь двоичного числа в псевдослучайные последовательности.

Выходы элементов ИЛИ 6 подключены к К-входовому элементу И 7. Выход эл мен та И 7 соединен со сче тным входом счетчика 8, к входу управления которым подключен выход элел ента И 4, Входы которого присоединены к разрядам сдвигово-45 го регистра 2.

При необходимости увеличения степени

К, в которую возводится число, увеличивается соответственно число блоков 2, 3, 4, 5.

Лля обеспечения модуля коэффициента

-Ц взаимной корреляции порядка 2 после— довательностей на входах элемента И 7 входы 3 -го сумматора по модулю два р-ой группы 3 (3 = 1,2, ..., Ц р 1,2,...,к-1) приссепинены к выходам

9,M у т — Х разрядов. регистра 2 (9 < и 4., 1" — Á и ), сумма по модулю два состояний которых в первом такте совпадает с состоянием }. -ro разряда

) сдвиговсго регистра в Щ -ом такте, для которого выполнено состношеиие 3Ф Ь y( а для сумм пс модулю два состояний выходов 1 сумматоров р-oN группы 3, совпадающих В суммами по модулю два состс яний Д,..., g -ых разрядов регистра 2 (П 4 ...dq 6 Л ) выполнено соотношение

g + g . ц .

Устройство работает следующим обраЗОМ.

С помощью К преобразователей g -разрядное двоичное число, содержащееся в регистре 1, преобразуется в К псевдослучайных последовательностей, которые имеют максимальный период, равный 2 -1

П тактов, математические сокидания, пропорциональные содержащему регистра 1, и модуль коэффициента взаимной корреляции порядка 2 (. Псевдослучайные последовательности с Выходов элементов ИЛИ 6 преобразователей поступают на К-Входовый элемент И 7, выполняющий операцию умножения последовательностей. К выходу элемента И 7 подключен счетчик 8, коммути руемый на максимальный период регистра

2 и Воспроизводящий в двоичном коде результат операции возведения двоичного числа в К-ую степень. Коммутация счетчика 8 осуществляется сигналом, поступающим с выхода т(-входового элемента И 4, подключенного к разрядам сдвигового регистра 2.

Применение Q --разрядного сдвиговсго регистра с обратной связью и (К-1) групп сумматоров по модулю два для преобразоВания g разрядного ЦВОичнОГО числа В

К линейно независимых (с погрешностью порядка 2 ) псевдослучайных последовательностей, период которых равен 2

К тактов, позволяет производить операцию возведения в К-ю степень с помощью элемента И за 2 — 1 тактов с погрешностью порядка 2

При заданной точности вычислений быстродействие данного устройства превышает быстродействие известных стохастических машин.

Формула изобре тения

Устройство для возведения двоичных чисел s квадрат, содержащее счетчик, счетный вход которого через элемент И соединен с выходами блока элементов

ИЛИ, первая и вторая группы входов которого соединены с выходами первого и второго коммутаторов соответственно, первые группы входов которых соединены с выходами регистра числа ссответствеино, о т л и ч а ю ш е е с а тем, что, с целью повышении быстродействии устройства, оно содержит рекуррентный регистр сдвига, блок сумматоров по модулю два, первый и второй блоки элементов И, выходы которых подключены ко вторым груп- % пам входов первого и второго коммутаторов соответственно, входы первого блока элементов И подключены к первой группе выходов рекуррентного регистра сдвига соответственно, вторащ группа выходов ко- о торого соединена со входами блока сумматоров по модулю два соответственно, выходы которого соединены со входами вто» рого блока элементов И соответственно, управлиюший вход счетчика соединен с последним выходом первого блока элементов И.

Источники информации, принятые во внимание при экспертизе:

1. Яковлев В. В., Федоров Р. Ф., Стохастические вычислительные машины, Л., Машиностроение, 1974.

2. Авторское свидетельство СССР

N 305482, кл. Cj 06 Q 7/16, 1 971.

Составитель A. Карасов

Редактор Н. Каменская Техред Э. Чужик Корректор М. Демчик

Заказ 5797/4О Тираж 826 Подписное

llHHHIIH Государственного комитета Совета Министров СССР по делам изобретений и открытий

1 13O35, Москва, )К-35, Раушскаа наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектнаи, 4