Следящий делитель частот

Иллюстрации

Показать всеРеферат

628488

О П И С А-Н-И -Й

ИЗОБРЕТЕН Ия

Союз Советских

Социалкстиыеских

Республик (6)) Дополнительное н авт. свил-ву (22) Заявлено 04.01.77 (21) 2438189/18-24 с присоединением заявки № (23) Приоритет— (43) Опубликовано 15.10.7&.Бюллетень № 38

2 (51) М. Кл.

Ст 06 F 7/52

H OS К 23/ОО

f ваудерстеенныН хамхтет

Саейтв Иенхатроа CCCP ае делан изобретеие» и етеаиткй (53) УД) 681.327 (088.8) (45) Дата опубликования описания 24.08.78 ! (72) Авторы

P. A. Воробель, В. Б. Дудыкевич, Т. Г. Галамвй изобретения и И. И. Уланова (71) Заявитель (54) СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ЧАСТОТ

Устройство относится к области вычиолительной техники.

Известно делительное устройство, содержащее схему управления, два двоичных делителя частоты и реверсивный регистр, поразрядно связанный потенциально-импульсными логическими вентилями типа И с каждым из делителей (1) Известное устройство обладает слож- то постыл и низкой точностью.

Наиболее близким техническим решением к данному изобретению является сгздепций делитель частот, содержащий реверсивный счетчик, вход вычитания которого т5 соединен с первым входом делителя, и счетчик, причем разрядные выходы реверсивного счетчика и счетчика подключены соответственно к первым и вторым входам элементов И группы t2j .

Однако следяший делитель частот име ет низкую точность, кроме того, дегимая частота должна быть меньше частоты делителяя. 25

11ель изобретения — повышение точности деления и расширение диапазона обрабатываемых частот.

Ътя этого предлагаемы@ делитель содержит блок сложения, первый вход которого подключен к второму входу делителя, а второй вход — к выходу элементов И группы, выход блока сложения подключен к входу сброс счетчика и входу сложения реверсивного счетчика.

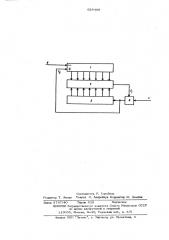

На чертеже представлена структурная схема предлагаемого слешпцего делителя.

Следящий делитель состоит из реверсивного счетчика 1, группы 2 элементов

И, счетчика 3 и блока сложения 4.

Вход вычитания реверсивного счетчика

1 является первым входом делителя, первый вход блока сложения 4 является вторым входом делителя, вход блока сложения 4 соединен с выходом группы элеменroe И 2, выход которого соетинен с входом счетчика 3 и входом сложения реверсивного счетчика 1, разряды последнего подключены к первым входам группы эле2 1 7 (1) где Х вЂ” чясгогя, подаваемая ня вход ( дели геля;

3 <- частота следования импульсов на выходе группы 2, определяемая ссотноц(ением и„-

Я 27

1tf где — число, содержащееся в счетчи1;

N < — коэффициент пересчета счетчиков

1 и 3. 20

На основании выражений (1), (2) для частоты 1 получим х ипм

2 (3)

Установившийся режим наступает при 25 равенстве частот у и 1, поступающих на входы счетчика 1 (у — частота, поступаюшая на вычитающий вход счетчика 1)

Х ж к 7 (4) М

Х

Z,= — Х т7 (5)

При оценке длительности переходного процесса в предлагаемом делителе урявне- 35 ние скорости накопления Е (4 ) в данном делителе имеет вид

4Е(О x ° и т7 (6)

Если при t „ (О) =* О, то, разделяя 0 переменные в выражении (6), получаем

Х Й,„1(. И,„

En — ° (7) х.й -yz, Рассмотрим частный случай, когда число K(4 } нарастает or 2 (О) =0 при до максимального значения при (((y K(J) Ц -1 Это соответству-. ет входным сигналам х = g, .-1,(ц,„ и у 1. Время Т, за которое переменная (. ) достигает уровня Q g

Щ при 1 (>> 1, равно

) (o,vn -0и Я - 1) (8)

Продолжительность переходного процес- 55 са в случае, когда динамическая погрешоткуда

6294 535( ментов И 2, вторые входи(которой связянь(с разрядами счетчика 3.

Устройство работает следуюшим образ((м.

Б исходном состоянии триггеры счетчика 1 находятся в нулевом состоянии. (-1яс- тога ня выходе блока 4 сложения равна ность ((е ((реп()(ц(яе т (>!(((о(с) KB, I(rя (+ - l ) и у 1 ряба((я

Т = Ч (0,7 — 1 ) фактов (9)

11о в извеютном устройстве д.-(игел( ность переходного процесса определяется коли чес твом та к гов заведомо мен ып ей чя". оты, т. е. у; в предлагаемом устройстве установившийся режим возможен при х.а у, длительность переходного процесса определяется количествсм тактов заведомо большей частоты. Г!оскольку количество тактов переходного процесса в обеих схемах одинаково, то длительность переходного процесса в предлагаемом делителе всегда меньше, чем в известном, т.е. бьп-.тродействие его больше

Г1огрешность округления в предпагаьмом делителе уменьшена в И „„ раз по сравнению с известным, т.е. достигается повышение точности делителя в Я„1 раз.

Кроме того, в предлагаемом(следи(цем делителе результат деления представляет собой частное от деления меньшей частоты на болыпую, что невозможно осущест вить при помощи известного делителя, в котором установившийся режим возможен лишь при условии х > у, т, е. предлагаемый делитель обладает расширенными функциональными возможностял(и.

Формула изобретения

Следящий делитель частот, содержаший реверсивный счетчик, вход вычитания которого соединен с первым входом целителя, и счетчик, причем разрядные выходы реверсивного счетчика и счетчика подклю чены соответственно первым и вторым входам элементов И группы, о т л и ч аю щ е е с я тем, что, с целью повышения точности деления и расширения диапазона обрабатываемых частот, делитель содержит блок сложения, первый вход которого подключен к второму входу делители, а второй вход — к выходу элементов И группь(, выход блока сложения подключен ко входу "сброс" счетчика и входу сложения реверсивного счетчика.

Источники информации, принятые во внимание при экспер тизе:

1, Лвторское свидетельство СССР

¹ 160906, кл. С 06 Я 7/16, 1967.

2. В. П. Лацчеев. Цифро-частотные вычисли тельные устройства. М, Энергия, 1976, с. 54.