Приемное устройство в системах асинхронного сопряжения цифровых сигналов

Иллюстрации

Показать всеРеферат

© Й В-: :. А Н И Е

ИЗОБРЕТЕН Ия

СО102 СОВФтски1

Социалистических

Республик

<и628619

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свиа-ву(22) Заявлено 18.05.77 (2l) 2486813/18-09

2 (51) М. Кл.

Н 04 3 1/02 с присоединением заявки №Гасударственнай квинтет йвета Мннвтрае CCN в делам нэобретаннй н вткрмтнй (23) Приоритет— (43) Опубликовано 15 10 78оюллетень № .38 (53) УДК 621.376. .56(088.8) (45) Дата опубликования описания 25.08.78

И. Т. Картюшов (72) Автор . изобретения (71) Заявитель (54) ПРИЕМНОЕ УСТРОЙСТВО В СИСТЕМАХ АСИНХРОННОЮ

СОПРЯЖЕНИЯ ЦИФРОВЫХ СИГНАЛОВ

Изобретение относится к электросвязи и может использоваться в многоканальных системах связи для передачи асинхронных импульсных последовательностей, Известно приемное устройство в системах асинхронного сопряжения цифровых сигналов, содержащее посцбдовательно соединенные первые элементы ИЛИ, HET и запоминаюший блок, другой вход которого через последовательно соединенные щ генератор с автоподстройкой и фазовый детектор соединен с выходом первого элемента НЕТ, декодер команд, первый и второй выход которого соответственно сое. динены с первыми входами второго и тре- 11 тьего элементов НЕТ, выходы последних соединены соответсгвенно с другими входами первых элементов ИЛИ и НЕТ, причем выход генератора с автоподстройкой соединен с другим входом фазового детек M торв (11.

Однако известное приемное устройст эо в системах асинхронного сопряжения цифровых сигналов обладает)недостаточно высокой помехоустойчивостью приема, так 25 как искажение двух или более команд приводит к сбою цнкловой синхронизации.

С целью повышения помехоустойчивос ти в предлагаемое приемное устройство в системах асинхронного сопряжения цифровых сигналов введены второй элемент

ИЛИ и триггер, причем первый и второй выходы декодера команд соединены соответственно с йервым и вторым входамн второго элемента ИЛИ, выход которого соединен с первым входом триггера, другой вход которого соединен с выходом фазового детектора, а выход триггера соединен с вторыми входами второго и третьего элементов НЕТ.

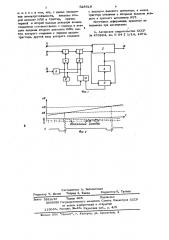

На фиг. 1 представлена функщкональная электрическая схема предлагаемого приемного устройства в системах асинхронного сопряжения цифровых сигналов; на фиг. 2 - временные диаграммы, пояс1пцошие работу устройства.

Приемное устройство в системах асинхронного сопряжения цифровых сигналов содержит последовательно соединенные первые элементы ИЛИ 1, HET 2 и запо628619 минающий блок 3, другой вход которого через последовательно соединенные генератор 4 с автоподстройкой и фазовый детектор 5 соединен с выходом первого элемента НЕТ 1, декодер 6 команд, его

Первый и второй выходы соответственно соединены с первыми входами второго и третьего алементов НЕТ 7 и 8, выходы которых соединены соответственно с дру гимн входами первых элементов ИЛИ 1 и HET 2, причем выход нер тор 4 с 10 автоподстройкой соединен с другим входом фазового детектора, второй элемент ИЛИ

9 и триггер 10, причем первый и второй выходы декодера 6 команд соединены со ответственно с первым и вторым входами второго элемента ИЛИ 9, выход последнего. соединен с первым входом триггера

10, другой вход которого соединен с выходом фазового детектора 5, а выход трил, гера 10 соединен с вторыми входами второго

20 итретьегоапементов НЕТ7 и 8,нaвxoд 11 подается разуппотненный информационный сигнал, на вход 12 - тактовая частота записи из блока, на вход 13 - коды команд стаффингов, кроме того, устройство

25 содержит выход 14.

Приемное устройство в системах асинхронного сопряжения цифровых сигналов работает следукнцим образом.

Информационный сигнал с входа 11 за30 писываетса в запоминающий блок 3 при помощи тактовой частоты записи, поступающей с входа 12 через, первый алемент ИЛИ 1 и первый элемент НЕТ 2

75 на первый вход запоминающего блока 3, Декодер 6 команд из последовательности чередующихся команд с входа 13 выделяет парные команды одного знака и в случае пары отрицательных команд формирует

40 на своем первом выходе сигнал, производящий дополнительную запись в запоминающий блок 3 через разрешенный второй элемент HET 7 и первый алемент ИЛИ 1.

В случае обнаружения пары положительных

45 команд сигнал со второго выхода декодера 6 команд через разрешенный третий элемент НЕТ 8 запрещает первый алемент

НЕТ 2 на время, равное одному периоду импульсов записи, а следовательно тор»

50 мозит запись информации в запоминаюший блок 3. В обоих случаях вкпючается генератор 4 с автоподстройкой и плавноперестраивает на один период считывающую поспедовательность импульсов на втором входе эапоми-. 55 наюшего блока 3 в ту илп иную сторону (в зависимости от знака команды), Эта перестройка происходит за время несколько меньшее периода формирования ,парных команд. В момент, когда сдвиг между частотами записи и считывания до стигнет величины 2Й, фазовый детектор

5 выключает перестройку генератора 4 с автоподстройкой и взводит триггер 10, при атом разрешаются второй и третий элементы НЕТ 7 и 8, которые пропускают первую же обнаруженную парную команду от декодера 6 команд. Эта же команда через второй элемент ИЛИ 9 сбрасывает триггер 10. Элементы HET 7 и 8 запрещаются и не пропускают от декодера 6 команд все последующие парные команды, образовавшиеся в результате помех в канале связи, до тех пор, пока не произойдет отработка уже принятой команды, и не взведется триггер 10.

На фиг, 2, а показано изменение фазы частоты считывания относительно частоты эаписиЬф Ц, а на фиг. 2,3 - соответству.юшаа ему структура команд, формируемых в передающем устройстве. По достижении разности фаэ величины +,2 и формируются парные команды (++ или --). При меньших фазовых сдвигах формируется чер мдуюшаяся последовательность команд (+ » + - +).

Поскольку после прихода парной команды приемное устройство, на все время отработки атой команды блокирует свой вход и открывает его лишь незадолго до прихода следующей парной команды (фиг.

2, r), то любые искажения, в том числе и одиночных команд фиг. 2, в), не при водят к сбою цикловой синхронизации.

Таким образом, в данном приемном устройстве повышается по мехоустойчивость приема, что позволяет осуществлять надежную связь на радиолиниях с дефицитом энергетики и высоким уровнем поI мех. формула изобретения

Приемное устройство в системах асин» хронного сопряжения цифровых сигналов, содержащее последовательно соединенные первые алементы ИЛИ, HET и запоминающий блок, другой вход которого через последовательно соединенные генератор с автоподстройкой и фазовый детектор соединен с выходом первого алемента НЕТ, декодер команд, первый и второй выходы которого соответственно. соединены с первыми входами второго и третьего элементов НЕТ, выходы которых соединены соответственно с другими входами первых алементов ИЛИ и НЕТ, причем выход генера тора . автоподстройкой, соединен с другим .входом фазового детектора, о т л и ч a