Устройство синхронизации с дискретным управлением

Иллюстрации

Показать всеРеферат

..-. «ч

ll с л (62Фб44

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

It АВТОРСКОМУ СВИДВТИЛЬСТВУ (б!) Дополнительное к авт. свил-ву (22) Заявлено 28.04.77 (21) 2481э30/18-09 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 25,10.78. Бюллетень № 39 (45) Дата опубликования описания 12.09.78 (51) М. Кл.

Н 04 1 7/10

Государстеенный неметет

Саввта Мнннстрев СССР ее делам нзебретеннй и атнритнй (53) УДК 621.394. .662 (088.8) (72) Автор изобретения

Т. С. Хабаров (71) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ С gNCKPETHblM УПРАВЛЕНИЕМ

Изобретение относится к электросвязи и может быть использовано в аппаратуре передачи двоичной ннформацйи.

Известно устройство синхронизации с дискретным управлением, содержащее формирователь входных импульсов, выход которого под- Ю ключен к одному из входов фазового дискри-, минатора, к друтим входам которого подклю- . чены соотве ствующке выходы соответствующего каскада делителя частоты, а выходы фазового дискриминатора подключены соответственно к первым входам элементов И и "Запрет", к вторым входам которых подключены соответствующие выходы преобразователя, управляемого задающим генератором, а также элемент

ИЛИ (1). т5

Однако такое устройство обладаеФ недостаточной точностью синхронизации.

Цель изобретения — повышение точности синхронизации.

Для этого в устройство синхронизации с дискретным управлением, содержащее формирователь входных импульсов, выход которого подключен к одному иэ входов фазового дискриминатора, к другим входам которого подключены соответствующие выходь1 соответствующего каскада делителя частоты, а выходы фазового дискриминатора подключены соответственно к первым входам элементов И и Запрет", к вторым входам которых подключены соответствующие выходы преобразователя, управляемого задающим генератором, а также элемент ИЛИ, введен триггер, при этом выход элемента Запрет" подключен к входу первого каскада делителя частоты, выход которого подключен к входу второго каскада делителя частоты через элемент ИЛИ, к другому входу которого подключен выход триггера, к входу которого подключен выход элемента И, причем элемент ИЛИ вьпюлнен в виде "исключающее ИЛИ".

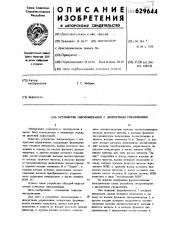

На чертеже изображена функциональная электрическая схема устройства синхронизации с дискретным управлением, Оно содержит формирователь 1 входных импульсов, выход которого подключен к одному иэ входов фазового дискриминатора 2, к другим входам которого подключены соответствующие выходы соответствующего каскада 3 делителя частоты 4, а выходы фазового дискриминатора 2 подключены соответственно к

629644

ПНИИПИ Заказ 6082 42 Тираж 763 Подписное

Филиал ППП Патент". г. Ужгород, ул, Проектная, 4 первым входам элементов И 5 и "Запрет" 6, к вторым входам которых подключены соответствующие выходы преобразователя 7, управляемого задающим генератором 8, а также элемент ИЛИ 9, триггер 10, при этом выход 5 элемента "Запрет" 6 подключен к входу первого каскада 11 делителя частоты 4, выход которого подключен к входу второго каскада 12 делителя частоты 4 через элемент ИЛИ 9, к другому входу которого подключен выход трнг-4р гера 10, к входу которого подключен выход элемента И 5, причем элемент ИЛИ 9 выполнен в виде "исключающее ИЛИ". Элементы И

13 и 14 образуют фазовый дискриминатор.

Устройство работает следующим образом.

В режиме опережения на выходе элемента

И 13 появится импульс, под действием которого будет запрещен один из высокочастотных импульсов последовательности, транслируемой элементом "Запрет" 6, и фаза регистрирующих эо импульсов на выходе соответствующего каскада 3 делителя частоты 4 сместится в сторону отставания на величину выбранного шага коррекции.

В режнме отставания импульс появляется 2S на выходе элемента И 14, и вызывает появление на выходе элемента И 5 импульса, расположенного в середине между импульсами, поступающими на элемент "Запрет" 6 с задающего генератора 8, что, в свою очередь, приведет 30 к переключению триггера 10 в противоположное состояние. В результате последовательность импульсов, транслируемая элементом ИЛИ 9, проинвертируется, причем момент инверсии произойдет посередине между значащими момен-чч тами импульсов с выхода первого каскада 11 делителя частоты 4, а фаза регистрирующих импульсов сместится в сторону опережения на величину шага коррекции.

Применение предлагаемого устройства синхронизации с дискретным управлением позволяет расширить область значений точности синхронизации без применения более быстродействующих и, следовательно, более дорогих логических элементов.

Формула изобретения

1. Устройство синхронизации с дискретн™ управлением, содержащее формирователь входных импульсов, выход которого подключен к одному из входов фазового дискриминатора, к другим входам которого подключены соответствующие выходы соответствующего каскада делителя частоты. а выходы фазового дискриминатора подключены соответственно к первым входам элементов И и "Запрет", к вторым входам которых подключены соответствующие выходы преобразователя, управляемого задающим генератором, а также элемент

ИЛИ,отличающееся тем, по, с целью повышения точности синхронизации, в него введен триггер, при этом выход элемента Запрет" подключен к входу первого кас сада делителя частоты, выход которого нодклйчен к входу второго каскада делителя частоты через элемент ИЛИ, к другому входу которого подключен выход триггера, к входу которого подключен выход элемента И.

2. Устройство по п. 1, о т и и ч а вщ е е с я тем, что элемент ИЛИ выполнен в виде "исключающее ИЛИ".

Источники информации, принятые во внимание при экспертизе:

1. Шляпоберский В. И. Основы техники передачи дискретных сообщений. М., "Связь", 1973, с. 253.