Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Н двтОРСкОМУ Саидиедьауау (11) 63 191 2 (6)) Дополнительное к авт. свил-ву в2 ц (22) Заявлено 29.08.75 (2) )2168851/18-24

Я 06 г 3/04 с присоединениек; заяв H .. .о (23) Приоритет (43) Опубликовано 08,11,78Б.;.ллетень Kr 41 (45) Дата опубликования описания 28 0< 78

Государственный комитет

СОВВт& Merrcrpas СССР оо делам нзабретеннй и открытнй

Ро) У. 1 681.327. . 1 1 (088. 8) ю. М. Крючков, ю. Г. Лиививи и о. A. Поввов

r (72) Авторы изобретения

{71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВВОЙА ИНФОРМАЦИИ

Изобретение относится к области вычислительной техники и может быть использовано в устройствах числового программного управления.

Известно устройство для ввода информации, содержащее генератор, регистр, мультиплексор, блок кодирования, блок управлениятдешифратор и блок исключения нулей в старших разрядах (1).

Наиболее близким по технической сущности к изобретению является устройство для ввода информации, содержащее блок считывания, соединенный с блоками контроля и адреса, выходы которого соединены с первыми входами соответствуюших блоков памяти, вторые входы которых подключены к соответствующим входам первого коммутатора, вход и выход которого подключены к блоку адреса (21.

Недостатком таких устройств является низкая надежность, Белью изобретения чвляется повышение надежности устройства.

Поставленная цель достигается тем, что в предложенное устройство введены, регистр и второй коммутатор, первый вход которого соединен с выходом блока адреса, второй вход — с соответствующим выходом первого коммутатора, а выходс первым входом регистра, второй вход

5 еоторогo подключен е Выхоту блока считывания, а выход — к третьим входам блоков памяти.

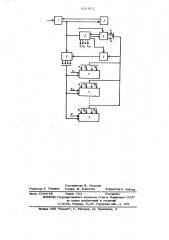

На чертеже представлена структурная схема устройства.

10 Устройство содержит блок считывания

1, блок контроля 2, блок адреса 3, первый коммутатор 4, регистр 5, второй коммутатор 6 и блоки памяти 7.

Устройство работает следующим обраi 5 зом.

Код адреса, считанный с перфоленты, поступает с блока считывания 1 в блок адреса 3. С .выхода блока адреса на первый коммутатор 4 поступает сигнал при.20 знак адреса", который разрешает прохож« пенне сигналов на вход коммутатора 4.

С выходов коммутатора 4 начинают поступать сигналы, которые через коммутатор 6 опрашивают регистр 5 и произво631 912 4 ется запись следующих декад регистра 5 в соответствующие разряды блоков памя— ти 7, начиная со старшего. Последней опрашивается та декада буферного регист ра 5, в которую записана последняя цифра числа по данному адресу. Блок контроля 2 осуществляет контроль информации на четность.

Устройство для ввода информации, со держашее блок считывания, соединенный с блоками контроля и адреса, выходы ко1S торого соединены с первыми вхопами соответствующих блоков памяти, вторые входы которых подключены к соответствующим входам первого коммутатора, вход и выход которого подключены к бло20 ку адреса, о т л и ч а ю ш е е с я тем, что с целью повышения надежности устройства, в него введены регистр и второй коммутатор, первый вход которого соединен с выходом блока адреса, 25 второй вход - с соответствующим выхФдом первого коммутатора, а выход - с первым входом регистра, второй вход которого подключен к выходу блока считывания, а выход - к третьим входам блоков памяти.

Источники информации, принягые во внимание при экспертизе:

1. Патент США ЪЬ 3749896, 06 Р 3/14, 1973.

2. Авторское свидетельство СССР, 14 318025, Cj 06 P 3/04, 1971, дят запись поступающей информации в соответствующий блок памяти 7 с помощью соответствующих сигналов адреса Ar

А111, поступающих с блока адреса 3.

После прохождения сигналов по всем разрядным шинам Р, - Р с коммутато

И ра 4 поступает в блок адреса 3 сигнал по которому осуществляется стирание пре дыдушего адреса, запись нового адреса, сброс регистра 5 и установка s исходное >6 состояние коммутатора 6.

При поступлении числовой информации с блока считывания 1 блок адреса 3 по каждой считанной цифре выдает сигнал

"признак цифры, который, поступая на вход коммутатора 6, переключает его.

Сигналы с выхода коммутатора 6 выбирают очередную декаду в регистре 5 для записи кода считываемой цифры. Таким образом осуществляется последовательно .запись в декады регистра 5 числовой ин— формации данного адреса.

При считывании кода следующего апре са регистр 5 переключается с записи информации на ее неренись в блоки памяти 7

Сигнал с выхода соответствующей разрядной шины коммутатора 4 управляет коммутатором 6 аналогично операции с читыв&ния цифр, flpg этом сигнал с Вы» ЗО

xDtl8 KoMb4 у".атора 6 производит опр Ос geкады регистра 5, следукнцей за той, на которой остановилась запись цифр. Содержимое этой декады записывается в разряд, соответствующий считанному адресу блока памяти 7, Аналогично осушествляформула изобретения

631 912

Составитель В. Меделян

Редактор Л. Утехина Техред Я. Борисова Корректор Л. Яебоща

Заказ 6344/48 Тираж 784 Поцпжное

UHHHIM Государственного комитета Совета Мщщстров СССР по делам изобретений и открьгщй

113035, Москва, Ж-35, Раушскаа наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4