Устройство для преобразования кодов с одного языка на другой

Иллюстрации

Показать всеРеферат

Союз Соввтсних

Социалистических

Республик

ОП ИСАНИЕ

ИЗОВРИтИНИЯ К АВТОРСКОМУ СВИДВТЕЛЬСТВУ 631931 (6!) Дополнительное к авт. свид-ву (22) Заявлено 22.04,77(2!) 2478391/18-24 с присоединением заявки № (23) Приоритет (43) Опубликоваио05.11.78.Бюллетень № 41 (45) Дата опубликования описания 10.11.78

2 (5!) М. Кл.

G 06 F 15/38

Гюоудврстаенный комитет

Соаата Мнннстроа СССР оо делам нэооретеннй н открытий (53} УДК681.325 (088.8}

В. А. Бородаев и Ю. В. Трудов (72) Авторы изобретения (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

КОДОВ С ОДНОГО ЯЗЫКА НА ДРУГОЙ ео!

Изобретение относится к вычиспитейь,ной технике и может быть испопьзовано при создании быстродействующих операцион ных систем дпя обработки информации.

Известно устройство дпя перевода с одного языка на другой, содержащее многоуровневую память и специапизированные процессоры, в том числе процес« соры синтаксического разбора и перекодироки, оптическое устройство считывания входной информации и экран отображения переведенного отрывка текста (1).

Однако такое устройство сложно и . требует значитепьных затрат оборудования.

Из известных устройств наиболее близким по технической суп ности к изобрете-.нию является устройство (2! содержащее ре.З1 гистр приема, входы которого через группу элементов И соединены со входами эо устройства, а выходы через дешифратор подкпючены к адресным входам бпока памяти, выходы которого через регистр выдачи соединены с выходами устройства.

2

Устройство позволяет сравнивать входное спово со словами, записанными в первом блоке памяти, и воспроизводить эквивапентное ему спово из второго блока памяти, Однако испопьзование двух блоков памяти и невозможность сопоставлении входного слова не топько с эквивапентным словом, но и эквивалентной поспедоватепь ностью слов сужают область применения устройства.

Цепью изобретения является упрощение устройства и расширение его функционапьных возможностей эа счет обеспечения сопоставления входного спова эквивапентной поспедоватепьностью спов.

Поставленная цепь достигается тем, что предложенное устройство содержит два эпемента И и допопнитепьный разряд в регистре выдачи. Единичный и нупевой выходы допопиитепьного разряда регистра выдачи подключены соответственно к первым входам первого и второго эпементов И, вторые входы которых соединены с управляющим входом устройства.

3 631931 4

Выход первого эпемента И соединен со счетным входом регистра приема, выход второго элемента И - с управляющими входами элементов И группы. Вход допойнитепьного разряда регистра выдачи сое- Ю динен с управляющим выходом блока памяти.

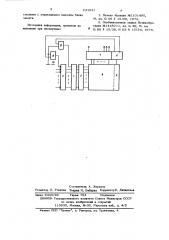

Структурная схема устройства дана на чертеже.

19

Оно содержит регистр 1 приема, выпопненный в виде регистра-счетчика; группу элементов И 2, дешифратор 3, блок 4 памяти, каждая ячейка которого снабжена разрядом 5 конца поспедова» тепьности, выход которого соединен с входом дополнитепьиого разряда 6 регистра выдачи 7, элементы И 8,9.

Устройство работает спедуюшим Ьб- З разом.

В исходном состоянии регистры .1 и 7 находятся в нулевом состоянии.

Единичный сигнал с нупевого выхода дополнительного разряда 6 регистра 7 открывает эпемент И 9. Сигнал с управпяюшего входа 10 через элемент И 9 поступает на управпяюшие входы группы элементов И 2 и производит запись входного слова в регистр 1. По смысповому Зй содержанию входного слова на регистре 1 дешифратор 3 формирует сигнал адреса эквивапентного слова ипи начальный адрес эквивалентной поспедоватепьности, кбто= рый поступает в блок 4 памяти. В соответствии с этим адресом на регистр 7 считывается первое слово эквивалентной поспедоватепьности, Разряд конца последовательности считываемого слова содержит единицу, если считываемое слово не является последним в эквивалентной поспедоватепьности, и содержит нуль, если считываемое спово является последним в эквивалентной последовательности. Сигнал с разряда 5 конца последовательности поступает на доцопнитепьный разряд регистра 7, устанавливая его либо в 1 (выходное слово не явлются концом эквивапентной последовательности), либо и О (выходное спово»конец эквивапент» ной нос педоватепьности). Если содержимое донопнитепьного разряда регистра 7 равно единице, то сигнап с единичного выхода открывает эпемент И В и следуюший сигнап со входа 10 поступает через

Я эпемент И 8 на счетный вход регистра 1 и увепичивает его содержимое на единицу, Дешифратор 3 формирует адрес очередноro слове, которое вместе со своим эна чением разряда конца последовательности считывается на регистр 7. Если при этом дополнительный разряд регистра 7 установится в единицу, то устройство работает аналогично описанному выше.

Еспи содержимое дополнительного разряда регистра 7 равно нулю, то единичный сигнап с нулевого выхода допопнитепьного разряда открывает элемент И 9 по уп равпяющему сигналу со входа 10, регистр ,принимает очередное входное слово.

Б дальнейшем цикл работы устройства повторяется. Эквивалентная последовательность выходных спов может состоять из одного слова, если разряд конца последовательности этого слова равен нулю

Предпоженное устройство праще известных устройств, так как в нем применен один блок памяти. Кроме того, оно позволяет сопоставить входное слово иа одном языке не топько с эквивалентным словом на другом языке, но и последовательностью эквивалентных спов, что расширяет его функциональные воэможноц ти.

Форму па изобретения

Устройство дпя преобразования кодов

С оодднноогго о яяззыыкка а нна а ддррууггоойй, содержашее регистр приема, входы которого через группу эпементов И соединены со входами устройства, а выходы через дешифратор подключены к адресным входам блока памяти, выходы которого через регистр выдачи соединены с выходами устройства, отпичающееся тем,что,с целью упрощения устройства и расширения его функционапьных возможностей за счет обеспечения сопоставления входного слова с эквиванентной поспедоватепьностыо слов, оно содержит два эпемента И и допопнитепьный разряд в регистре выдачи; причем .единичный и нупевой выходы дополнительного разряда регистра выдачи подключены, соответственно к первым входам первого и второго элементов И, вторые входы которых соединены с управ пяюшим входом устройства; выход первого эпемента И соединен со счетным входом регистра приема; выход второго элемента И подключен к управпякнцим вхомм элементов И группы, а вход дс попнитепьного разряда регистра выдачи

631931

Составитель А. Жеренов

Редактор Л. Утехина Текред Н. Бабурка Корректор Е. Дичинская

Заказ 6345/49 Тираж 784 Подписное

11НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж:-35, Раушская наб., g. 4/5

Филиал ППП Патент, г; Ужгород, уп. Проектная, 4 соединен с управляюшим выходом блока памяти, Источники информации, принятые во внимание при экспертизе:

1. Патент Франции %2101495, M. кл. G 06 F 15/00, 1972.

2. Опубликованная заявка Бепнкобританин %1448211, кл. G 4Н, М. кл.

G 06 F 15/38, Н 03 К 15/24. 1976.