Устройство для суммирования в системе остаточных классов

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сомз Советских

Социалистических

Республик i iI 631 935.(6l) Дополнительное к авт. свид-ву (22) Заявлено 29.04.77(21) 2483517/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано05. 11.78.Бюллетень №41 (45) Дата опубликования описания,10.11.78 (51) M. Кл.

6 06 G 7/14

Государственный комитет

Совете Министров СССР по делам иэооретений и открытий (53) УДК 681.335 (088,8) М. В, Синьков, А. И. Закидапьский, В. A. Впадимиров и Н. Б. Нифонтов (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ В СИСТЕМЕ

ОСТАТОЧНЫХ КЛАССОВ

Изобретение относится к области вычислительной техники, в частности к уст ройствам математического модепирования, и может быть использовано дпя сложения в произвопьного. числа 2 входных сигналов в системе остаточных классов.

Известны устройства (lf, представляющие собой сумматор дпя одновременного сложении нескольких двоичных спагаемых, состоящие из комбинационнътх схем, регистров сложения и выходных регистров.

Однако такие устройства спожны, что снижает их надежность и быстродействие.

Наиболее бпизким техническим решением к изобретению является устройство дпя суммирования s системе остаточных классов, содержащее весовые резисторы, ключи, источники попожитедьного и отрицатепьного опорных напряжений и операционный усипитедь, неинвертирующий вход которого через входные масштабные резисторы подсоединен к соответствующей группе входов устройства, а выход через резистор обратной связи подкпючен к его инвертирующему входу и явпяется выходом устройства(2).

Недостатком устройства.явпяются низкое высокое быстродействие и относитепь- ° ная сложность.

5 Цепью изобретения является повышение быстродействия и упрощение устройства.

Поставленная цепь достигается тем, что предпоженное устройство содержит анаt0 лого- цифровой преобраэоватепь АЦП, вход которого соединен с неинвертирующим входом операционного усипитепя, а группа выходов подкйючена к управляющим входам соответствующих,кпючей, 15 по два информационных входа каждого из которых подсоединены соответственно к источникам поножитепьного и отрицательного опорных напряжений, а выходы через весовые резисторы подкпючены к инвертируккцему входу операционного ycRпитепя.

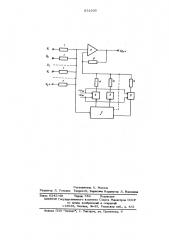

На чертеже приведена функциональная схема устройства.

3 631935

Устройство состоит иэ нескольких идентичных входных масштабных резисторов l„ oTo e epee AL111 2 соединены с управляющими входами ключей 3. Устройство содержит также суммирующий one- 5 рационный усилитель 5, в цепи обратной связи которого включен резистор 6 обратной связи и весовые резисторы 4. Неинвертирующий вход усилителя 5 соединен с резисторами 1. to

Устройство работает следующим образом.

Входные сигнапыЦ 0,,0 @ суммируются на резисторах . . Результат суммирования поступает на неинверти» l5 рующий вход усилителя 5 и на вход

АЦП 2. Двоичный код на выходе АЦП 2 используется дпя управления ключами 3, коммутирующими резисторы 4.

Проводимость цепи обратной связи 20 усилителя 5 равна ф 2о, а полная проводимость, подключенная к инвертирующему усипитепю 5 равна

f +y,+2Д.+ Фу. +... - Я ут2 у.

Напряжение на инвертирующем входе 2$ равно

U )+О ы U (2

О „,„и„,<2 4 +4- г ) ге

У где $ - состояние АЦП 2.

Величина напряжения на неинвертирующем входе определяется иэ выражения вится в соответствие напряжение-Uì то при

2е

rn (j + 4 ) ) Я и . > rn .

1=1

АЦП 2 будет в 1-м состоянии и его двоичный код представляет число, Так как на выходе усилителя 5 устанавливается такое напряжение, при котором (1 = 0 то получаем л

ze

"" Е ;-U г о „„+О,„ 2 +4-2 ) г 2Е ипи далее после простых преобразований

Таким образом, устройство выполняет операцию модупарного суммирования 2

6 величин и может быть использовано в системе остаточных классов.

Устройство дпя суммирования в системе остаточных классов, содержащее весо30 вые резисторы, ключи, источники положительного и отрицательного опорных напряжений и операционный усилитель, неинвертирующий вход которого через входные масштабные резисторы подсоединен к соо1

35 ветствующей группе входов устройства, а выход через резистор обратной связи подключен к его инвертирующему входу и является выходом устройства, о т и ич а ю щ е е с я тем, что, с цепью по4О вышения быстродействия и упрощения устройства, оно содержит аналого-цифровой преобразователь, вход которого соединен с неинвертирующим входом операционного усилителя, а группа выходов подключена

45 к управпяющим входам соответствующих ключей, по два информационных входа каждого иэ которых подсоединены соответственно к источникам положительного и от50 рицатепьного опорных напряжений, а выходы через весовые резисторы подкпючены к инвертирующему входу операционного усилителя.

Источники информации, принятые во

55 внимание при экспертизе:

1. Авторское свидетельство СССР

%188151, М.Кд, Cj 06 F 7/50, 1966.

2. Авторское свидетельство СССР

%462179, М. Кп. G 06 F 7/50, 1975. его ге

О.

1 1

-ге

4 4

E— ь гдеЯ -сопротивление 1-го резистора 1 и прй

Я =М ° .. вР

1 г " 2е

ge

Е u„.

У, ге

Если подставить вместо U значение

2umm

U,-ï; о„, в выражение U> то, получаем

4 ги f-и г

Если ширина Мванта по напряжению равна — —,а нулевому состоянию ста

2Uw

20„„2Е ивЫХ Е п1 (23++4)U

1 пт.

Формула изобретения

V, Составитель A. Маслов

Редактор Л. Утехина Техред М. Борисова Корректор Л. Василина

Заказ 6345/49 Тираж 784 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4