Нейристор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

631943 (61) Дополнительное к авт. свил-ву (22) Заявлено 20.04.77 (21) 2479102/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.11.78Зюллетеиь М. 11 (45) Дата опубликования описания 10.11.78 (5l) М. Кл.

6 06 G 7/60

Гооударстоенный номнтет

Совета Мнннстроо СССР оо делам нзобретеннй н открытий (53) УДК681.335 (088.8) О. L1. Баранцева (72) Автор изобретения

Запорожский индустриальный институт (71) Заявитель (54) НЕЙРИСТОР

Изобретение относится к области выечиспитепьной техники и автоматики, 1

Известно устройство дпя модепирования нейрона, содержащее входную ннтег рирующую цепочку, резисторы, конденсаторы и тиристоры jlj. Однако, это устройство не обпадает достаточной устойчивостью при воздействии на него внешних возмущений.

Наиболее близким техническим решением к изобретению явпяется устройство, которое содержит нейристорные пинии, информационные входы которых подкпючены к соответствующим информационным входам нейристора, а информационные выходы - к соответствующим информационным выходам нейристора, причем каждая нейристорная пиния содержит резисторы(2)., Однако .это устройство обладает недостаточным в ряде случаев быстродействием, технопогия изготовления нейристора спожна и параметры его трудно воспроизводимы и зависят от внешних воздействий . (температурных> излучения и т. д.).

U HBKо,изобретения явпяется BGBsBII8 нне быстродействия, воспроизводимости и устойчивости параметров к внешним воздействиям.

Постав пенная цепь достигается тем, что предложенный нейристор содержит конденсатор, одна обкпадка которого соединена со входом тактовых нмпупьсов нейристсра, а другая обкпадка подкпючена к одноименным входам нейристорных пиний, соответствующие вход-выходы разветвления и искпючения сигнапа которых соединены между собой. Нейристорные пинии содержат отражатепьные кпистроны, резонаторы которых в .каждой нейристорной пинии через петли связи соединены поспедоватеi=.1:о. Резонатор первого отражатепьного кпистрона через петлю связи подключен к информационному входу нейрнсторной пинии, резонатор пос пе дне го отражатепьного к пистрона через петлю связи соединен с информационным выходом нейристорной линии.

Отражатепь каждого отражательного кпистрона соединен через соответствующий

631943 резистор с отражатепями соседних отражательных клистронов. Отражатель первого отражательного кпистрона подключен ко входу питания отражатепя нейристорной линии, который явпяется одноимен- У ным входом нейристора, отражатепь последнего отражательного кпистрона сое динен со входом тактовых импульсов нейристорной пинии. Катоды отражательных клистронов объединены и через со. -- Il ответствующие резисторы подключены ко входу смещения нейристорной пинии, который является одноименным входом нейристора, Вход-выход разветвления сигнапа нейристорной пинии соединен с резона- тором соответствующего отражате пьного кпистрона, а вход-выход исключения сигнала нейристорной линии — с катодом соответствующего отражательного клистрона.

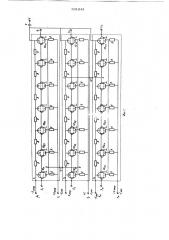

На фиг. 1 приведена принципиальная схема нейристора; на фиг. 2 — зависимость мощности P отражательного кпистрона от напряжения на отражатепе Е отр и напряжения смещения на отражателях отражательного кпистрона.

2$

Нейристор содержит нейристорные линии 1 -1„, конденсатор 2, информационные входы 3 — 3>, информационные выходы 4 — 4, вход тактовых импульсов

5, входы питания отражателя 6 — 6 и

1 ll входы смещения 7 «7, Нейристорная линия 1 содержит резисторы 8 и 9, отражатепьные кпистроны 10, вход-выход 11 исключения сигнала и вход-выход 12 разветвления сигнапа.

Нейристор работает следующим образом.

Перед приходом входного сигнала все отражательные клистроны 10 импупь-46 сами напряжения тактовой частоты, подаваемыми в цепи отражатепя, выводятся в состояние отсутствия генерации.

Напряжения смещения на отражателях кпистронов 10 устанавливают такой вели- чины, как показано на фиг. 2 где Е -, Е"

7 напряжения смещения на клистронах

10 - 10„> Ев Е -напряжения на кпистронах 10 - lO„E -Е -напряжение

3О на клистронах 10„„-10„п(изменение величины напряжений смещения на отражатепях кпистронов 10 достигается с помощью резисторов 8, вкпюченных в цепи отажателей), P

Я ъ

Под действием входного сигнала преI

Э вышающего его порогового значение, по нейристорной пинии 1 распространяется импульс, амплитуда и форма которого не зависят от формы входного сигнала. Распространение импульса происходит с постоянной скоростью, определяемой длитепьностью переходных процессов в кпистронах 10. При распространении импульса по линии I (при возбуждении каждого следующего кпистрона 10) смещение напряжения, образующееся на катодном резисторе 9 клистрона 10, переводит каждый предшествующий кпистрон 10 в состояйие отсутствия генерации (поспеднее обеспечивается распредепением величины напряжений смещения на отражателях. клистронов 10, показанным на фиг. 2).

Таким образом, вслед за распространяющимся импульсом распространяется зона, нечувствительная к внешним воздействиям.

Аналогично, соединение нейристорных пиний l вход-выходами 12 разветвления сигнала (соединение I-I) допускает распространение сигнала без уменьшения его вепичины топько в одну сторону по направлению к выходу нейристора. Соединение нейристорных пиний I вход-выходами 1 1 искпючения сигнала (соединение II-й ), передавая напряжение смещения на катодном резисторе 9 из одной нейристорной пинии1 в другую, тем самым создает запрет прохождения сигнапов по другой нейристорной пинии I .

Формула изобретения

Нейристор, содержащий нейристорные линии, информационные входы которых подключены к соответствующим информационным входам нейристора, а информационные выходы нейристорных линий соединены с соответствующими информационными выходами нейристора, причем каждая нейристорная пиния содержит резисторы, о т и и ч а ю шийся тем, что, с целью повышения быстродействия, воспроизводимости и устойчивости к внешним воздействиям, он содержит конденсатор, одна обкладка которого соединена со входом тактовых импульсов нейристора, а другая обкладка подключена к одноименным входам нейристорных пиний, соответствующие вход-выходы раз-ветвления и искпючения сигнала которых соединены между собой, а нейристорные линии содержат отражательные клистроны, резонаторы которых в каждой нейристорной линии через петин связей сое-.

> динены поспедоватепьно; резонатор первого отражательного кпистрона через петша связи подключен к информационному вхо631943 ду нейристорной линии, резонатор последнего отражательного клистрона через петлю связи соединен с информационным выходом нейристорной пинии; отражатепь каждого отражательного клнстрона соединен через соответствующий резистор с отражателями соседних отражательных кпистронов; отражатепь первого отражательного кпистрона подключен ко входу питания отражателя нейристорной линии, который является одноименным входом нейристора; отражатепь последнего отражательного клистрона соединен со входом тактовых импульсов нейристорной линии, катоды отражательных кпистронов обьединены и через соответствующие резисторы подключены ко входу смешения нейристорной линии, который является одноименным входом нейристора; входвыход разветвления сигнала нейристорной линии соединен с резонатором соответст вующего отражательного кпистрона, а вход-выход исключения сигнала нейристорной пинии соединен с катодом соответст» вующего отражатепьного клистрона. ! е

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетепьство СССР

Мо373737, М, Кл. G 06 G 7/60, 1971, 2. Авторское свидетельство СССР

%395862, М. Кп. G 06 G 7/60, 1971.

631943 свц

I ЕР ЕЕ ЕУ Е9

I ì J п à 9 J !

Составитель Г. Сорокин

Редактор Л. Утехина Техред М. Петко Корректор Е. Йичинскиая

Заказ 6345/49 Тираж 784 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по дедам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Фияиая ППП Патент, r. Ужгород, ул. Проектная, 4