Ячейка памяти на мдп-транзисторах

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К . АВТОРСКОМУ СВИДВТЙЛЬСТВУ 631987

Союз Советских

Соцналнстннесннх

Реснублнн (6!) Дополнительное к авт. свиа-ву

2 (5l> М. Кл.

Ст 11 С 11/40 (22) Заявлеяо02.04.75 (21} 2119934/24 с присоединением заявки № (23) Приоритет

Гввударвтввввнй квивтвт

Свввта Мввюрве CCCP вв двин взвврвтввхв а втхвнтвй (43) Опублиыовано05.11.78.Áþëëeòåíü № 41 (5Ç) УДК 681.327. .66 (088.8} (46} Дата опубликования описаний 05.11.78 (72) Автор изобретения

И, Н, Кабанов (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ НА МДП-ТРАНЗИСТОРАХ

Изобретение относятся к области автоматнкн н вычислительной техннкн н может быть использовано прн построенин полупроводннковых эапомннающнх устройств уняверсальных н спепналнэнрованных вычислительных машин. 5

Известна ячейка памяти на МДП-транзнсторахе содержащая первый транзнстор, исток которого соединен с корпусом, затвор — с истоком второго т внзнстора„а сток — с нетоком третьего транзнстора, N сток которого подключен к первой разрядной шине, а затвор — к адресной шине н затвору второго транзистора, сток которого соединен со второй разрядной шнной 1 .. Недостатком ячейкн является малое быстродействие и необходимость сложного трехуровневого. управляющего .на пряження по адресной шине.

Наиболее блнзкой по технической сущности к изобретению является ячейка памяти, содержащая первый транзистор, исток которого соединен с корпусом, затвор — с нстоком второго транэнстора, а сток - о нстоком третьего транзнстора, затвор которого подключен к первой адресной шине, а сток - к первой раз-. рядной шнне н стоку четвертого транзнотора, затвор которого соедннен со второй адресной шиной, а исток - с затвором второго транзистора, сток которого еоеннннен но второй реерннной шине (21.

Недостатком ее является большое количество оборудования.

Целью изобретения является упрощенне устройства, Эта цель достнгается тем, что в предложенной ячейке памяти затвор н сток второго транзистора соедннены соответственно с истоком н стоком первого транзнстора.

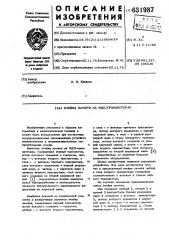

На чертеже приведена прннцнпиальная схема ячейки памятн.

Она содержит первый 1, второй 2 н третий 3 транзисторы. Первая разрядная шина 4 соединена с истоком транзистора

3, затвор которого подключен к адрес= ной шине 5, а сток — к истоку транзистора 1 и затвору транзистора 2. Стоки транзисторов 1 н 2 соединень1 со второй

631987

Составитель Г. Милославский

Редактор Л. Утехина Техред М. Петко Корректор Д. Мельниченко

Заказ 6359/52 Тираж 675 Подписное

ЫНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5 филиал ППП Патент", r. Ужгород, ул. Проектная, 4 разрядной шиной 6. Емкость 7 предсталяет собой емкость затвора транзистора

1 и емкость истока. транзистора 2 на подложку 8, Транзис горы 1 - 3 представляют собой Й -канальные МДП-транэисто- У ры (принцип работы ячейки сохраняется и для р канальных МДП-транзисторов), Ячейка. памяти работает следуюшнм образом, В режиме хранения напряжение на ши- 16 иах 4 и 5 равно нулю. На шине 6 поддерживается высокое положительное напряжение достаточное для записи 1

На подложку, 8 подается небольшое отрицательное запирающее. напряжение, Ин- И формация, записанная в ячейку, хранится на ем кости 7, Ддя записи информации в ячейку памяти иа вины 4 и 5 подаются высокие положительные напряжения. Запись 1 в ® ячейку цроиэводится цри напряжении на шипе 6, равном иацряжению хранения, запись О - при нулевом напряжении на шине

6. Информация иа емкость 7 пост@п-.. аетт череэ открытый транзистор 2, После 39 осушествления записи напряжение иа шине 4 понижается до нуля, на шине 6 устанав мваегся напряжение хранения, а затем понижается до нуля напряжение на шине 5. В режиме считывания на шину 5 М подается высокое напряжение, Если в ячейку вацисана 1; то це,шинам 4 и

6 благодаря открытым "транзисторам

1 и 3 протекает ток считывания 1

При считывании 0 транзистор 1 эакриг, и ток считывания через ячейку не протекает.

Ячейка памяти проста и технологи чна в изготовлении, имеет небольшую площадь в интегральном исполнении и экономична вследствие небольшого числа

MQ П- гранэисторов.

Формула и з обретения

Ячейка памяти на МДПтранзисторах, содержащая первый транзистор, затвор которого соединен с истоком второго транзистора, а исток — co стоком третьего транзистора, затвор которого подключен к адресной шине, а исток - к первой разрядной шине, причем с ок второго .транзистора соединен со второй разрядной шиной, отличающийся -тем, что, с целью упрошення, в ией затвор и сток второго транзистора соединены соответственно с истоком и стоком первого транзистора.

Источники информации, принятые во внимание при экспертизе:

1. Патент США ¹ 3593037, кл, 307-238, 1970, 2, Авторское свидетельство СССР

¹ 529485, кл. Cj 11 с 11/40, 25.12,74,