Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

И ЗО БР ЕТЕ Н И ЯК АВТОРСКОМУ СВИДВТЕДЬСТВУ

< 631989

Сиз Сое те1емат

Соцетаямсттечасюе» ееасяубяия (61) Дополнительное к авт. свнд-ву

2 (5!) M. Кл (22) Заявлено29,09.76 (23)2406330/18-24 ! с присоединением заявки №

С 11 С 15/02 (23) Приоритет

Геотдарстевкевй кометет

Совете Мкккотрое СССР ео делам кэобретеевв я открытей (43) Опубликовано05.11.78. Бюллетень №41 (531 УДК 628.327. .6 (088,8) (4о) Дата опубликования описания 05.11.78

В. И. Караштин, Е, A, Румянцев, И, A. Новиков, В. В, Николаева-Терешкова, С. A. Шацилло и А. E. Аверкин (72) Автори изобретения (7! ) Заявитель (54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и может быть игпользоьано в качестве универсального логического автомата для автоматизированных систем управления, Известны логические запоминающие устройства, содержащие матрицу нч двухотверстных трансфлюксорах, болышие и малые отверстия которых прошиты вертикальными и горизонтальными шинами 1 .

В этих устройствах реализация логических функций организована сложным образом я требует спедиального программного управляющего блока, Наиболее близким по технической сущности к изобретению является логическое запоминающее устройство, содержащее матричный накопитель иа двухотверстных трансфлюксорах, большие и малые отверстия ксторых прошиты адресными и числовыми шинами, адресные и числовые шины больших отверстий соединены через коммутатор.с источником постоянного тока, числовые шины малых отверстий соединены со входами логических элементов Запрет, выходы которых соединены с обмотками выходных реле, и генератор разнополярных импульсов 2 .

Белью изобретения является повышение надежности устройства путем умен щения амплитуды тока считывания, Эта цель достигается тем, что в устройстве управляющие контакты двух реле соединены с выходами генератора разнополярных импульсов, управляющие контакты других реле соединены попарно, начала адресных шин малых отверстий соединены с замыкающими и размыкаQ ющими контактами входных и выходных реле, а концы их объединены в группы.

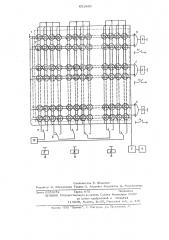

На чертеже представлена принципиальная электрическая схема устройства. Устройство содержит матричный накопитель 1 на двухотверстных трансфпюксорах 2. Большие отверстия трансфлкксоров прошиты адресными (вертикальными) и числовыми (горизонтальными) шиНами, подключенными через коммутатор

3 к источнику 4 постоянного тока.

Малые отверстия трянсфлюксоров прошиты числовыми аннами, coeIIIIIIeIIIII>III

6З1989 со входами логических элементов Запрет 5, выходы которых подключены к обмоткам выходных реле 6, и адресными . шинами, начала которых соединены с замыкающими и раэмыкающими контактамн

7 входных реле 8 и замыкающими и размиакающими контактами 9 выходных реле 6.

Управляющие контакты двух любых реле, напрнмер, первого входного и последнего выходного, соединены с выходами генератора раэнополярных импульсов

1О управляющие контакты остальных реле соединены попарно, а концы каждых четырех адресных шнн, соединенных с замыкающими и раэмыкающими контактами двух реле, управляющие контакты которых разобщены, соединены друг с другом эамынающне контакты 11 выходных. реле 6 соединены с выходными контактами устройства.

Устройство работает следующим образом.

По заданной программе с помощью коммутатора 3 и источника постоянного тока 4 трансфлюксорам задается начальная намагниченность заблокировано (0 ) или разблокировано" ("1 ) .

Запускается генератор разнополярных имнульсов 1О, Происходит опрос трансфлюксоров, которые прошиты адресными шинами, соединенными в данный момент времени с управляющими контактами реле при этом входной сигнал считывания подается в пеночку, состоящую из после1 довательно соединенных „адресных шин, образуемых контактами входных и выходных реле. Поэтому ток считывания накопителя равен току считывания одного тра нсфлюксора.

При считывании информации с трансфлюксора, на котором записана 1, в числовой шине наводится ЭДС выхода; если на трансфлюксоре записан О"ЗДС выхода не наводится.

Реалнзапия булевых функпий проводится в базисе ЗапретИиэъюнкция-Инверсия». Например, для реализации элементарной конъюнкции на две переменных необходимо: записать 1 на трансфлюксоре, находящемся в пересечении адресной шины, соединенной с замыкякьщим контактом входного реле одного сигнала и числовой шины, соединенной с прямым входом элемента Запрет, "; записать 1" H& трансфлюксоре, находящемся в пересечении адресной шины, соединенной с размыкающим контактом входного реле другого сигнала и числовой шины, соеди35 ненной с запрещающим входом элемента

"Запрет ., Обратная связь в устройство введена для реализации сложных функций методом суперпозипин и функднн Память с запреИ том".

Формула изобретения

39 Логическое запоминающее устройство, содержащее матричный накопитель на двухотверстных трансфпюксорах, большие и малые отверстия которых прошиты адресными и числовыми шинами, адресные

2% и числовые шины больших отверстий соединены через коммутатор с источником постоянного тока, числовые шины мальх отверстий соединены со входами пЬгических элементов "Запрет", выходы кото36 рых соединены с обмотками выходных реле, и генератор разнополярных импульсов, о т и и ч а ю щ е е с я тем, что, с целью повышения надежности устройства путем уменьшения амплитуды тоМ ка счнтывания, в нем управляющие контакты двух реле соединены с выходами генератора раэнополярных импульсов, управляющие контакты других реле соединены попарно, начала адресных шин

46 малых отверстий соединены с замыкающими и размыкающнми контактами входных и выходных реле, а концы их объединены в группы.

Источники информации, принятые во

® внимание при экспертизе:

1, Балашов Е. П. и др. Многофункциональные запоминающие устройства. М„

Энергия", 1972, с. 36.

2. Авторское свидетельство СССР @ N522522,,кл. Я 11 С 11/08, 1974.

6319ЕЕ

Составитель С. Шаиилло

Репактвр И Мархсвсквн Техреп O. Анпренкс Ксрректср рх. П1енввнчвнкс

Заказ 6359/52 Тираж 675 Подписно е

Ц11ИИПИ Государственного ко иитета Совета Министров СССР по делаки изобретений и открытий

1 13035, Москва, Ж-35, Рау.нская нлб,, д. 4/5

Филиал ППГ1 "Патент, г. Ужгород, ул. П1 оектная,