Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

И АЗТОРСКОМУ СВИДВТИЛЬСТВУ

<» 631991

Союз Советских

Соцналюстнчешик

Республик

1 (51) М. Кл.

Ст 11 С 17/00 (6l} Дополнительное к авт. свид-ву (22) Заявлено11.04.77 {21)2475457/18-24 с присоединением заявки № (23) Приоритет (43} Опубликовано05.11.78.Бюллетень № 41 (45} Дата опубликования описания 05.11.78 рраудвретаеииьй NONfTfT

6овата Минастроа СССР за делам мзабрвтеиай

il ОТМРытмй (53) УДК 628.327, .6 (088.8) (72) Авторы К. И. Диденко, К. Г. Карнаух, А. Н. Конарев, Г. Н . Полященко, изобретения А. А. Ручинский н И, С. Шандрин

Специальное конструкторское бюро систем автоматического управления (71} Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области автоматики н вычислительной техники н может быть использовано в попупроводниковых ЗУ.

Известны ЗУ на биполярных и многоэмнттерных транзисторах с матричной организацией запоминающих элементов 1(Д °

Однако этн устройства характериэутотся большой потребляемой мощностью.

Наиболее.близким техническим решением к изобретению является ЗУ, содер- 1о жатцее адреснйй регистр, выходы которого соединены с входами дешифраторов, соответствующий вход одного нэ которых соединен с одним нэ входов элемента ИЛИ, выход которого подключен к одним иэ входов адресного регистра н другого дешифратора, информационные, адресные шины, шины записи и считывания, Выходы одного иэ дешнфраторов соединены с одними иэ вхоаов наколитепя (2). 2о

Однако в таком устройстве сложна аппаратурная реапнзацня управления адресными шинами накопителя н недостаточно использована воэможность снижения пот ребпяемой мощности за счет уменьшения входных токов адресных шин накопителя.

Одними нз основных потребителей тока в попупроводниковых. запоминающих элементах на биполярных многоэмнттерных транзисторах являются адресные входы, например, дпя элементов. К 155 РУ1 один невыбранный адресный вход потребляет 11 ма. В режиме. хранения информации все адресные входы запоминающего элемента оказываются невыбранными (потенциал логического 0 ), вследствие чего токи, потребляемые по этим входам, ма кснма льны., Цепью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что предложейное устройство содержит коммутатор, дополнительные элементы

ИЛИ. н элемент НЕ вход которого соединен с выходом элемента ИЛИ, а выходс первыми входами дополнительных элементов ИЛИ, вторые входы которых соединены с выходами одного из дешифраторов. Выходы дополнительных элементов

ИЛИ соединены с соответствующими входами накопителя, выходы которого соединены с входами коммутатора, управляющий вход которого подключен к одному из выходов адресного регистра. %

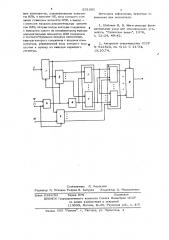

На чертеже представлена структурная схема устройства.

Устройство содержит адресный реracrp 1, дешифраторы 2, 3, элемент 4

ИЛИ, накопитель 5, элемент 6 НЕ, до- и полнительные элементы 7 ИЛИ, коммутатор 8, адресные шины 9, информационные 10, шины записи 11 и шины считывания 12.

Накопитель 5 может быгь построен И

as интегральных полупроводниковых запоминающих элементах памяти, например

K 155 РУХ, таким образом, что все одноименные адресные входы этих элементов объединены в соответствующие ад% ресиые шины накопителя, которые через элементы 7 ИЛИ соединены соответственно с выходами дешифратора 3 адреса.

Информационные входы запоминающих элементов накопителя; подключены соот- 39 ветственно к выходам дешифратора 2 информации, а выходы запоминающих элементов накопителя соединены соответственно с информационными входами коммутатора 8, 36

Устройство работает следующим o6 разом, В режимах записи или считывания на входы элемента 4 ИЛИ поступают управляющие сигналы Считывание (шина 12} или "Запись (шина 11). В результате на выходе последнего форми.руется сигнал,. стробирующиф работу ðåгистра 1 и дешифратора 3. Сформированный ара этом на выходе дешифратора 3 адрес ячейки памяти через элементы 7 4@

ИЛИ поступает иа адресные шины накс пителя 5. При этом в режиме считывания на всех выходах дешифратора 2 формируется код считывания, поступающий на информационные входы запоминающих элементов накопителя 5.

В режиме записи в соответствии с кодом адреса запоминающего элемента, поступающим от регистра .1, информаци ей (шина 10) и стробирующим сигна- М лом Запись (шина 11) на дешифраторе

2 производится выборка соответствующего информационного входа накопителя 5.

Это обеспечивает, запись информации в выбранную ячейку памяти накопителя 5, Выдача информации из накопителя 5 на выход производится коммутатором 8 в соответствии с адресом запоминающего элемента, поступающим от регистра ), В режиме хранения информации на выходе элемента 6 HE формируется сигнал, который через элементы 7 ИЛИ возбуждает все адресные шины накопителя 5.

На информационных входах накопителя при этом устанавливается код считывания, так как отсутствует сигнал Запись" (шина 11). При этом одновременно считываются все ячейки памяти накопителя

5 (полупроводниковые запоминающие элементы на биполярных многоэмиттерных транзисторах допускают многократное считывание без разрушения хранимой инФормации). Считанная информация на выход не поступает, так как отсутствуют адресные сигналы на управляющем входе коммутатора 8 от регистра 11.

Введение в устройство элементов 6

НЕ, 7 ИЛИ .и коммутатора 8 обеспечи» вает режим одновременного считывания всех ячеек запоминающих элементов накопителя устройства (ток потребления при этом по каждому адресному входу запоминающих элементов -6 0,28 ма) о без выдачи информации на выход устройства, т,е. в режиме хранения инфермации ток потребления адресных шин накопителя уменьшается в и 0,28 3S раз.

Кроме того, введение в схему коммутатора позволяет проводить адресную выборку выходов запоминающих элементов накопителя в режимах записи.или считывания, используя вместо индивидуальных клапанов для каждого адресного входа каждого запоминающего элемента (как в известных устройствах) по одному каналу для всех одноименных адрес ных входов всех запоминающих элементов накопителя.

Таким образом„предлагаемое устройство по сравнению с известными существенно проще и экономичнее.

Форм ула и з обретения

Запоминающее устройство, содержащее адресный регистр, выходы которого соединены с входами,дешифраторов, соответствующий вход одного из которых соединен с одним из входов элемента

ИЛИ, выход которого подключен к одним из входов адресного регистра и другого дешифратора, выходы одного нз дешифратрров соединены с одними из входов накопителя, информационные, адресные шины, шины записи и считывания, о т л и ч a— ю щ е е с я тем, что, с целью повышения надежности устройства, оно содер

Источники информации ° принятые R0 вним а ни е при эксп ерти зе:

1. Шебанин В. В. Интегральные функциональные узлы для запоминающих устройств, Советское радио, 1976, с. 12-24, 40-42.

631991 6 жит коммутатор, дополнительные элементы ИЛИ и элемент НЕ, вход которого соединен с выходом элемента ИЛИ, а выходс первь:ми входами дополнительных элементов ИЛИ, вторые входы которых соединены у с выходами одного из дешифраторов; выходы дополнительных элементов ИЛИ соединены с соответствующими входами накопителя, выходы которого соединены с входами коммутатора, управляющий вход которого под«а 2. Авторское свидетельство СССР ключен к одному из выходов ацресного N 522523, кл. Q 11 С ll/34, регистра. 18. 10.74.

Составитель Л. А мусьева

Редактор Л. Утехина Техред Н. Бабурка Корректор Д. Мельниченко

Заказ 6359/52 Тираж 675 Подписное

11НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., n. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проекгная, 4