Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

ОП И(:А,НИEИЗОБРЕТЕНИЯ ""632О73

Саюз Севатсннк

Соцнаиистнчасння

Респубпнн

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 060577 (21) 2484029/18-21 с присоединением заявки %— (233 Приоритет— (43) Опубликовано 05.1178. Бюллетень № 41 (45) Дата опубликования описания 10.11.78 (54) М. Кл.

Н 03 К 5/18

Государственный комитет

Совета Министров СССР, по делаи изобретений и открытий (53) УДК б21. 374. 32

:(088 ° 8) (22) Авторы изобретения

B.Â.Ãoðøêoâ и А ° А.Сулиманов

Pl) Заявитель (54) ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к импульсной технике.

Известен Фазовый дискриминатор, содержащий входной смеситель, на вы- . ходы которого поданы дискриминируемый и опорный сигналы, гран.очные частотные фильтры, через которые выходы смесителя подключены к фазовому раэличителю, выполненному на туннельных диодах, и накопительный фильтр нижних частот, включенный на выходе Я .

Однако точность работы такого дискриминатора недостаточна.

Наиболее близким по технической сущности к изобретению является фазовый дискриминатор, содержащий фазовый раэличитель, входы которого соединены с шинами дискриминируемого и опорного меандрового сигналов, один из выходов соединен с первыми входамн логического элемента ИЛИ и триггера блокировки,а второй выход подключен к одному входу второго логического элемента

ИЛИ, формирователь сигнала рассогласования, один вход которого соединен с . шиной высокочастотного сигнала, два других входа которого подключены к выходам логических элементов ИЛИ, второй вход второго из которых соединен с выходом логического элемента.

И, первый вход которого соед н í с выходом триггера блокировки 2

Недостатком этого дискриминатора является недостаточный частотный диапазон дискриминации. целью изобретения является расширение частотно1о диапазона дискриминации.

Поставленная цель достигается тем, что в предложенный фазовый дискриминатор, содержащий фазовый различителЬ,,входы которого соединены с шинами дискриминируемого и опорного меандротвого сигналов, один из выходов соеди нен с первьми входами первого логического элемента ИЛИ и триггера блокировки, а второй выход подключен к .одному из входов второго логического элемента ИЛИ, формирователь сигнала рассогласования, один вход которого соединен с шиной высокочастотного сигнала,два других входа которого подклю . чены к выходам логических элементов

ИЛИ, второй вход первого из которых соединен с выходом логического элемента И, первый вход которого соединен с первым выходом триггера блокировки, введен дополнительный логический элемент И, первый вход которого соединен со вторым выходом триГ"

632073

30 гера блокировки и с дополнительным входом фазового различителя, второй вход соединен со вторым входом логического элемента И и шиной эталонного сигнала, а выход — со вторым входом второго логического элемента ИЛИ.

Второй вход триггера блокировки соединен со второй шиной эталонного сигнала.

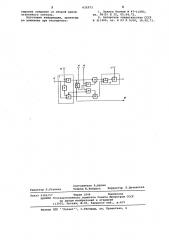

Структурная схема фазового дискриминатора приведена на чертеже.

Фазовый дискриминатор содержит фазовый различитель 1, состоящий из логических элементов Й 2, 3 и фазоиивертора 4, триггер блокировки 5, формирователь сигнала рассогласования 6, состоящий из триггера 7 и 35 логического элемента И 8, логические элементы И 9, 10 и логические элемен TH ИЛИ 11»12.

Фазовый дискриминатор работает следующим образом. И

Яа входную шину 13 поступают импульсы фронтов принимаемых посылок.

Кроме того, на фазовый дискриминатор подаются сигналы, соот вет ствующие временным интервалам эталонных носылок. На шину 14 поступает симметричный меандр с длительностью периода равной длительности опорной посылки, На шины 15 и 16 соответственно поступают импульсы, соответствующие середине и границам эталонных посылок, а на шину 17 - высокочастотные импульсы. С выхода 18 снимается сигнал рассогласования, Если импульс фронта окажется в первой половине эталонной посылки, он проходит на выход элемента И 3, в противном случае он проходит на выход элемента И 2.

Рассогласование между импульсом 40 на выходе элемента И 2 и следующим импульсом границы эталонных посылок соответствует величине фазового рас-согласования между принимаемым сигналом и эталонной посылкой при оста- 45 вании, а рассогласование между им-пульсом границы эталонных посылок и импульсом на выходе элемента И 3 соответствует величине фазового рассогласования между эталонной посыл--. 60 кой н принимаемым сигналом при опережении.

Импульс с выхода элемента И 2 проходит через элемент ИЛИ 11 на вход установки триггера 7 формирователя величины рассогласования и на установку триггера 5 блокировки, на выходе которого формируются разрешающий потенциал для элемента И 10 и запрещающий потенциал для элементов И 3 и 9.

Следующий импульс границы посылки, 60 подаваемый на шину 16, проходит через элемент И 10 и элемент ИЛИ 12 на вход сброса триггера 7. На выходе триггера

7 формируется разрешающий потенциал, подаваемый на элемент И 8, на другой 65

1 ф вход которого проходят высокочастотные импульсы с шины 17. Таким образом, на выходе формирователя величины рассог ласования 6 образуется пачка импульсов.

Импульс середины посылки, поступающий с шины 15, подается на сброс триггера блокировки 5,на выходе которого формируются разрешающий потенциал для элементов И 2 и 9 и запрещающий потенциал для элемента И 10.

При опережении следующий импульс границы посылки, подаваемый на шину

16, проходит через элементы И 9 и

ИЛИ ll на вход установки триггера 7.

Импульс с выхода различителя 1 проходит через элемент И 9 на сброс триггера 7, и на выходе последнего форми руется разрешающий потенциал. При этом так же, как и при отставании, иа выходе формирователя величины рас согласоваиия 6 образуется пачка импульсов. Знак потенциала на выходе триггера 5 блокировки во время формирования выходной пачки импульсов сви" детельствует о знаке фазовой ошибки. ; другой функцией триггера блокиров" ки 5 является подача запрещающего потенциала на элемент И 3 при поступ ; ленни импульса отставания с выхода различителя 1. Это необходимо для ликвидации зоны неустойчивого равновесия вокруг точки рассогласов. ния

А на в пределах + —, где

6- величина постоянных преобладаний

g принимаемого сигнала.

Формула изобретения

Фазовый дискриминатор, содержащий фазовый различитель» входы которого соединены с шинами дискриминируемого и опорного меандрового сигналов, один из выходов соединен с первыми входами первого логического элемента ИЛИ и триггера блокировки, а второй выход подключен к одному из входов второго логического элемента ИЛИ, формирователь сигнала рассогласования, один вход которого соединен с шиной высокочастотного сигнала, а два других входа. подключены к выходам логических элементов ИЛИ, второй вход первого из которых соединен с выходом .логического элемента И, первый вход которого соединен с первым выходом триггера блокировки, о т л и ч а ю— шийся тем, что, с целью расширения частотного диапазона дискриминации, в него введен дополнительный логический элемент И, первый вход которого соединен со вторым выходом триггера блокировки и с дополнительным входом фазового различителя, второй вход — co вторым входом логического элемента И и шиной эталонного сигнала, а его выход соединен со вто-! рым входом второго логического элемента ИЛИ; второй вход триггера бло