Тестовый модуль для контроля параметров интегральных микросхем

Иллюстрации

Показать всеРеферат

О П Ъ Е

И ЗОЬРЕТЕ Н ИЯ

Союз Советских

Социалистиыеских

Республик (и)632967 (6l) Дополнительное к авт. свил-вуЛЪ 570856 (22) Заявлено28.04.77 {21) 2480157/18-21 с присоединением заявки №вЂ” (23) Приоритет

2 (51) М. 1(л

g 01 К 31/28

Гасударственай немнтет

Совета Инннстров СССР ле делам нзобратеннй н втнрытнй (43) Опубликовано15,11,78,Бюллетень ¹ 42 (53) УДК6 -1.317 .7 99(088. 8) (45) Дата опубликования описания 16.11.78 (72) Авторы изобретения

В. М. Дубовис, Ю. И. Ан онов и I0. H. Чернышев

{73) Заявитель

{54) тестовый мод ль для контРОля пАРАмЕтРов

ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

Изобретение относится к области элект- . роизмерительной техники и может быть использовано в устройствах для контропя пине йных интеграпьных микросхем.

Наиболее близким по технической сущности является известный тестовый мо- 5 дупь дня контроля параметров интегральных микросхем по авт. св, N0 570856, содержащий четыре операционных усилителя, резистивные детали напряжения и резистор температурной стабилизации. о .Недостатком этого тестового модупя явпяется невозможность измерения среднего входного тока смешения.

Бель изобретения — расширение функционапьных воэможностей путем обеспечения измерения среднего входного тока смешения.

8 предлагаемый тестовый модупь дпя контроля параметров интеграпьных микросхем введены три перекпючатепя, причем входные клеммы первого, второго и третьего перекпючатепей соединены соответственно с неинвертируюшим входом третьего операционного усилителя, выходом депитепя напряжения, через делитель напряжения — с выходом второго операциочного усипитепя> первые выходные клеммы первого, второго и третьего переключатепей соединены соответственно с общей шиной, инвертируюшим входом третьего операционного усипитепя и выходом третьего операционного усилителя, а вторые выходные кпеммы второго и третьего переключателей соединены соответственно с пеинвертируюшим входом третьего операционного усилителя и обшей шиной.

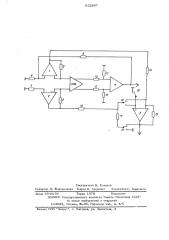

На чертеже приведена структурная схема тестового модуля.

Тестовый модупь дпя контроня параметров интегральных микросхем содержит четыре операционных усилителя 1-4, резисторы 5,6, резистор температурной стабилизации 7, депитепь обратной связи на резисторах 8,9, четыре депитепя напряжения на резисторах 10, 11, 12, 13, 14, 15, 16 17 и три группы контактов 18» 20.

632967

Тестовый модуль дпя контроля параметров интегральных микросхем работает спедуюшим образом. Режим испытуемой интегральной микросхемы (на чертеже не показана) устанавливается опера- У ционным усилителем 4, устанавпиваюшим равенство входных напряжений испытуемой интегральной микросхемы. Так как операционные усилители 1 и 2 идентичны и согласованы по своим параметрам, то . Ф к входам испытуемой интегральной микросхемы приложено лишь напряжение смешения нуля Ugg и выходное напряжение операционного усилителя 1 равно z ем s > Й СМ 6 вертируюшим входом третьего операцион: ного усилителя, выходом делителя напряжения, через депитепь напряжения — с выходом второго операционного усилителя, первые выходные клеммы первого, второго и третьего переключателей соединены соответственно с обшей шиной, инаф . вертируюшим входом третьего операционного усилителя и выходом третьего опе,рационного усилителя, а вторые выходные клеммы второго и третьего перекпючате4$ лей соединены соответственно с неинвертируюшим входом третьего операционного усилителя и обшей шиной. Ok! g СМ g, я Р где Rq = 10028

Выходные напряжения Eg и Ез на выходах операционных усилителей 1 и 2 равны

Где 75 Я =Я

На выходе операционного усилителя 3 действует напряжение ЕА. а так как Ц1 -- Ц = Я ц = Я ., то

Таким образом, выходное напряжение операционного усилителя З прямо пропорционально лопусумме входных токов.

При другом положении контактов контактных групп 18, 19, 20 производится измерение разности входных токов.

Введение трех контактных групп позвопяет повысить универсальность тестового модуля, депаетего пригоднымдляиэмерения всех типов операционных и дифференциальных усилителей.

Предлагаемый тестовый модуль не требует последовательного сбора тестовых схем дпя измерения параметров интегральных микросхем, не требует коммутации их измеритепьных цепей, приводяших к увепичению временных задержек, обусловленных переходными процессами в цепях коррекция, дает возможность измерения параметров интегральных микросхем без заполнения промежуточных результатов и вычислений, Формула изобретения

Тестовый модуль дпя контроля параметров интегральных микросхем по авт. св.¹570856 отличающийся тем, что, с цепью расширения функциональных возможностей путем обеспечения измерения среднего тока, в него введены три переключателя, причем. входные клеммы первого, второго и третьего перекпю. чатепей соединены соответственно с неин632967

Составитель В. Евпаков

Редактор Л. Жаворонкова Техред О. Андрейко Корректор С. Гарасиняк

Заказ 6546/36 Тираж 1070 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35э Раушская наб., д. 4/5 фипиап ППП Патент", r. Ужгород, уп Проектная, 4