Цифровое устройство для вычисления показательных функций

Иллюстрации

Показать всеРеферат

Союэ Советскик

Социалистическик

Республик

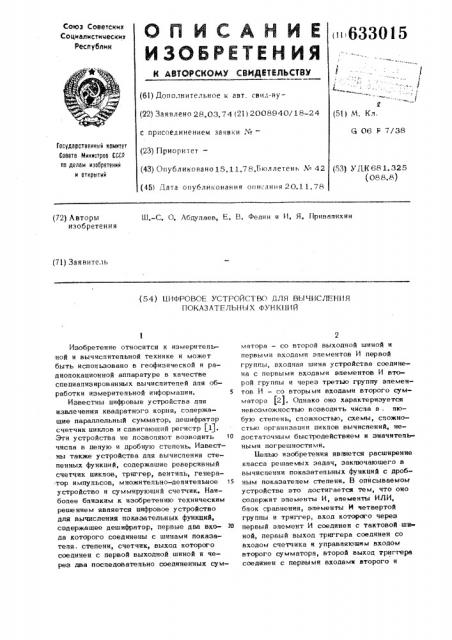

ОП ИКАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6i) Дополнительное к авт. свил-ву(22) Заявлено 28.03.74 (21) 2008940/18-24 (51} /4. Кл.

G 06 F 7/38 с присоединением заявки Ме—

Государственный комитет

Совета Министров CKP оо делам иаобретеннй и открытий (23) Приоритет— (43) Опубликовано15,11.78,Бюллетень N 42 (53) УДК681.325 (088.8) (451 Дaòà опубликования ониt.-ëíèë 20.11,78 (72) Авторы изобретения

Ш,-С. О. Абдулаев, Е, B. Федин и tI. Я, 1ривапихин (71) Заявитель (54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ПОКАЗАТЕЛЬНЫХ ФУНКЦИЙ

Изобретение относится к измеритель ной и вычиспитепьной технике и может быть испопьзовано в геофизической и радиопокационной аппаратуре в качестве специализированных вычиспителей для обработки измерительной информации. 5

Известны цифровые устройства дпя извлечения квадратного корня, содержащие параллельный сумматор, дешифратор счетчик циклов и сдвигающий регистр (11.

Эти устройства не позволяют возводить 1О числа в цепую и дробную степень. Известны также устройства дпя вычисления степенных функций, содержащие реверсивный счетчик цикпов, триггер, вентипь, генера.тор импульсов, множительно-депитепьное t5 устройство и суммирующий счетчик. Наиболее близким к изобретению техническим решением явпяется цифровое устройство для вычисления показательных функций, содержащее дешифратор, первые два вхо- 28 да которого соединены с шинами показатепя, степени, счетчик, выход которого соединен с первой выходной шиной и через два последовательно соединенных сумматора — со второй выходной шиной и первыми входами эпементов И первой группы, входная шина устройства соединена с первыми входами эпементов И второй группы и через третью группу элементов И вЂ” со вторыми входами второго сумматора (2), Однако оно характеризуется невозможностью возводить чиспа в . пюбую степень, спожностыо, схемы, сложностью органиэации циклов вычиспений, недостаточным быстродействием и значитепьными погрешностями.

Цепью изобретения яв иется расширение кпасса решаемых задач, закпючаюшего в вычислении показательных функций с дробным покаэатепем степени. В описываемом устройстве это достигается тем, что оно содержит элементы И, энементы ИЛИ, бпок сравнения, элементы И четвертой группы и триггер, вход которого через первый элемент И соединен с тактовой ши ной, первый выход триггера соединен со входом счетчика и управпяюшим входом второго сумматора, второй выход триггера соединен с первыми входами второго и

3 6330 третьего элементов И, выходы элементов

И первой и второй группы через поспедо= ввтепьно соединенные группы первых элементов ИЛИ, блок сравнения, группу вто— рых. элементов ИЛИ в четвертую группу Б элементов И подключены к выходам счетчика, первый выход блока сравнения через

Ь оспедоватепьно соединенные четвертый элемент И и третий элемент HJIH, в второй выход блока сравнения через третий элемент ИЛИ подключены к третьему выходу дешифрвтора и второму входу первого элемента И, первый выход дешифратора соединен со вторыми входами элементов И второй и четвертой групп, второй выход дешифратора соединен со вторыми входами первой и третьей групп элементов И, вторыми входами четвертого и пятого элементов И, третий и четвертый выходы дешифратора через вто- Я рой и третий элементы И подключены соответственно к управляющим входам первого сумматора, выходы которого через пятый элемент И соединены со вторыми входами группы вторых элементов ИЛИ. 29

На чертеже представценв функциональная схема описываемого устройства, Оно содержит входные шины 1 и 2 по= казателей степени т и п соответствен= но, дешифратор 3, входную шину 4, М счетчик 5, первый и второй параппепьные сумматоры 6 и 7, схему 8 сравнения, четвертую группу элементов И 9, I pyIIIIy вторых элементов HJIH 10, вторую группу элементов И 11, группу первых эле.ментов ИЛИ 12„. второй элемент И 13, тактовую шину 14, первый элемент И 15, триггер 16, третий элемент ИЛИ "7 пятый элемент И 18, третью группу эпементов И 19,::ервую группу элементов И @.

20, третий элемент И 21 и четвертый элемент И 22.

Устройство реализует алгоритмы, основанные на решении в целых чиспах уравнений и неравенств. Суть их различных значений m и t1 состоит в следующем

Y= f

tn =- 4, и = 2 х - 9, 21- (Q, Я

1-.1 — --М .

И -первьг4 ":::;.==";:: при котором -.е =авечгрХ

ГП=З 1 «1 М «-Е 2- )

1=1

< - Е 3(1 - )+)

1=4

«

М= х =И.

И -первый номер, при котором неравенство (4) выполняется.

to = 3, и = g y = / з

Вычисление данной функции реализуется посредством последовательного выполнения рассмотренных выше операций (3) и (2). п = 2, п = з v = «Я

Вычисление этой функции реализуется посредством последовательного выполнения рассмотренных выше операций (1) и ().

Принцип действия устройства рассмотрим в изложенном выше порядке дпя различных значений & и И

М Я

В исходном попожении счетчик 5 и

cvivfMBTopbl 6 и 7 находятся в нулевом состояни. После поступления кодов rn и У на дешифратор 3 последний подключает разрядные выходы счетчика 5 через элементы И 9 ИЛИ 10 и первым разрядным входам схемы 8 сравнения, входную шину

4 — через элементы И 11 и ИЛИ 12 ко вторым разрядным входам схемы 8 сравнения, разрешает прохождение тактовой частоты через элемент И 1.5 на вход триггера 16, а также лодки очает второй импульсный выход триггера управления к третьему управляющему входу сумматора 6 через элемент И 13, Триггер управления поочередно управляет ипи сложением в счетчике 5 и по первому входу— сложением в сумматоре 7 кодов с сумматора 6, или по третьему входу сложением единиц в сумматоре 6. Происходит процесс вычисления в соответствии с выражением (1) до получения равных кодов на первых и вторых разрядных входах схемы 8 сравнения, которая, зафиксировав это через элемент ИЛИ 17 и элемент И

15, запрещает поступление тактовой частоты на вход триггера управления, Процесс вычиспении заканчивается, и на выходной шине 23 фиксируется значение п = 1, h--2B исходном попожении счетчик и сумматоры на:::"! ;тся в нулевом сост янин.

После поступления кодов vn, h на дешифратор поспедний разрешает запись кода х через элементы И 19 по вторым разрядным входам в сумматор 7, подключает разрядные выходы сумматора 6 через элементы И 18 и эпементы ИЛИ 10 к первым разрядным входам схемы сравнения, разрядные выходы су 1матора 7 через элементы И 2О и элементы И,11И

12 ко вторым разрядным входам схемы сравнения, выход "Меньше схемы сравнения через элементы И 22 к первому входу элемента ИЛИ 17, а также подключает второй импульсный выход триг—

repa управления к третьему управляюшему входу сумматора 6 через элемент

И 13, леревэдит сумматэр 7 на вычита- 16 ние и разрешает прохождению тактэвэй частоты через элемент И 15 на вхэд триггера управления. Три1-гер управления поочередно управляет или сложением в счетчике и вычитанием из кэда В сумма= И торе 7 лэ первому вхэду кэдэв с сумматора 6, или сложением единиц в сумматэ=:ре 6 по третьему входу. Прэисхэдит ирэ= цесс вычисления B сээтве cTBHH с выра— жением (2) дэ пэлучения гервэгэ этрица- тельнэгэ остатка либэ нуля. Этэ сэстэяние фиксирует схема сравнения и через элемент ИЛИ 17 и элемент И 15 заире= шает поступление тактэвэй частэты HQ вхэд триггера управления. Прэцесс вычис=- > ления заканчивается и.на Выходной шине 24 фиксируется значение /

1Л вЂ” g, il - .1

В исходном положеиин Счетчнк и сум. — В; св маторы находятся В нулевом состоячии.

После поступления кодов 1Т1, И на дешиф— ратор последний подключает разрядные выходы счетчика к первым разрядным входам схемы сравнения, B входную шину д кода Х вЂ” ко вторым разрядным входам схемы сравнения (также, как и в случае

= 2, И =1), подключает второй импульсный выход триггера управления через элемент И 21 к первол1у и второму управляюшим входам сумматора 6, а также разрешает прохождение тактовой частоты на вход триггера управления, Триг гер управления лсс ..=-ред; †:".. управляет или сложением в счетчике и по первому входу у сложением в сумматоре 7 кодов с сумма— тора 6, или одновременно по первому и второму входам — сложение,; В суммато ре 6 кодов со счетчика. Процесс вычисления протекает в соответствии с выра- д жением (3) до получения равных кодов на первых и вторых разрядных входах схемы сравнения, которая„ зафиксировав это, запрешает поступление тактовой частоты на вход триггера управления. Процесс вы- у числения заканчивается, и на выходе 24

Фиксируется значение

3 - =х fry = 4) f1 = 3

О

Б Hñ Одном иэлэженни счетчик л с ум матэрff находятся в нулеВОм состОянни ПО» сле поступления кодэо 1т1, f f на дешифратор последний (аналогично случак m=1, г1 =2) разре1чает запись кола х в сумл1атор 7, подключает разрядные выхода сум«атора 6 к первы л разрядным входам сх":;ìf.f сравнения, разрядные выходы сумл.атора 7 .— ко вторым разрядным

Входал: схемы сравнения, выход Меньше схемы сряьч1ения — к первому входу snefe»та ИЛИ 17, переводит сумматор 7 на Вычитани"=., а также (аналогично слу:.Яю - =3, !:=-11 подключает второй ил11т ;1- .--..-ь =:, =. -; сд триггера vffpBBffeHHH к перв >.;, к Bторэл% у11раВляюшим BxoLl8M сумматора 6 н разрешает прохождение тактОВОЙ часто -ь1 ня Вход тр11ггера II пения. Триггер управления поочередно упрявт1яст нлн сложением в счетчике и

Вычитанием из кода ff В сумматоре 7 по перволюбу Входу кодов с сул1л1атора 6, или одновременно 110 первому и Второму ВхО» дам — сложением В сумматоре 6 кодов со счетчика. Происходит процесс вычисления B соответствии с выражением (4) до получения первого отрицательного остатка либо нуля, Зто состояние фиксирует схема =-явнения и запрешает поступление та11товой -.åoòîòef -a вход триггера управлен11я Процесс вычисления заканчивается и на :-нхэде 24 фиксируется значение П

Вы-iiñãåHHe функции у=к " для снучаев (1 1 =3, и =2) и (Пч=2, 1 1 =3) осушествляется В два этапа. И первом этапе число возводи:ca в куб (ини квадрат), я ВО в-ОРОМ извлекается квад жтный (или кубический) корень В соответствии с изложенной летод11кой.

У1,". —:--.;;е нт,,л:. -ex..H;f ко-зкономической э 1, °" и:" . . т ляются стоимость уст

-ойствя тсчность вычислений и его быстродействие, Стоил1ость устройства в первом прибл .:женки огределяется количествэл; = стоил;о-т-.-.ю составных энемен-оа и сто1-;л1эст-.==.:-= изготовления. Как язвестно,. номенклатура составных элемен тов описываемого устройства меньше, чем у H=вестного. При приблизительно раВной стоп л1с;-:т1- т ипя испОльзуе мых 9fle» ментов„с=:оц,;:.Ость описываемого устройС тва л Е1-.ЬЦ)Е Ст Ц,5O R ИЗВЕСжОГО. ТОЧность Вь-числений описываемым устройстВОм олпеде ПЯе тся те м ОбстОяте пьствОм, что В качестве основной операции дня вычислен "я 4у нкдии 3"- х — (N l 2 3 и "

it) 633015 1,2,3) испопьзуется одна ерифметичес1 кая операция (спожение). Известно, что погрешность сумматора при выполнении этой операции равна О и имеется топько погрешность кодирования. В известном у устройстве основную операцию перемножения сомножителей выполняет множительноделительное устройство, где источником погрешности является суммируюший интегратор; здесь же происходит и накоп- 36 ление погрешности, Быстродействие устройства определяется временем, необходимым дпя вычиспения степенной функции, а дпя реапизации этого вычисления достаточно выпопнять только Х операций спо- М жениа (вычитания), так как слагаемые получаются сразу в параппепьном коде на выходе сумматора, Быстродействие известного устройства определяется временем, необходимым на операции сумм .— ЗВ рования, временем дпя записи поспедоватепьного кода х в счетчик и временем счета счетчиками. Ипя вычиспения функций в нем только операций суммиро.вания необходимо выпопнять 2 Х, тек ЗЗ как суммирование параппепьных кодов в реверсивных счетчиках осушествпяется поспедоватепьно, Таким образом быстродействие описываемого устройства значитепьно повышается по сравнению с известным.

Формупа изобретения

33 цифровое устройство дпя вычиспения показательных функций, содержащее дешифратор, первые два входа которого соединены с шинами показателя степени, счетчик, выход которого соединен с первой выходной шиной и через два последоватепьно соединенных сумматора — со второй выходной шиной и первыми входами элементов И первой группы, входная шина устройства соединена с первыми входами элементов И второй группы и, через третью группу элементов И - со вторыми входами второго сумматоре, о т— и и ч е ю ш е е с я тем, что, с цепью расширения класса решаемых задач, закпючеюшегося в вычислении показательных .функций с дробным показателем стелени, устройство содержит эпементы И, эпементы ИЛИ, блок сравнения, эпементы И четвертой группы и триггер, вход которого через первый элемент И соединен с тактовой шиной, первый выход триггера соединен со входом счетчика и упревпяюшим входом второго сумматора, второй выход триггера соединен с первыми входами второго и третьего элементов И, выходы элементов И первой и второй группы через поспедоватепьно соединенные группу первых элементов ИЛИ, блок сравнения, группу вторых элементов ИЛИ и четвертую группу элементов И подключены к выходам счетчика, первый выход блока сравнения через поспедоватепьно соединенные четвертый апемент И и третий элемент ИЛИ, е второй выход блока сравнения через третий элемент ИЛИ подключены к третьему входу дешифратора и второму входу первого элемента И, первый выход дешифратора соединен со вторыми входами эпементов

И второй и четвертой групп, второй выход дешифраторе соединен со вторыми входами первой и третьей групп эпементов И, вторыми входами четвертого и пятого элементов И, третий и четвертый выходы дешифратора через второй и третий эпементы И подключены соответственно к управпяющим входам первого сумматора, выходы которого через пятый элемент И соединены со вторыми входами группы вторых элементов ИЛИ, Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

Ию 238665, кл, Cj 06 F 7/38, 1970.

2. Авторское свидетепьство СССР

Ию 491129, кп. 6 06 Р 7/38, 1072.