Устройство для контроля логических блоков цвм

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ 1»633019 (6!) Дополнительное к авт. свил-ву(22) Заявлено 23.08. 76 (21) 2398 926/18-24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано15. 11.78. Бюллетень hk 42 (45) Дата опубликования описания 28.11.78

2 (5!) M. Кл, G 06 F 11/04

Государственный номитет

Соеета Министров СССР по делам изобретений и открытий (53) УДК 68!.326.. 7 (088. 8) (?2) Автор изобретения

В, В, Бьшанов (?1) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ

БЛОКОВ llBN

Изобретение относится к автоматике н вычислительной технике н может быть использовано дпя контроля исправности цифровых интегральных схем.

Известно устройство дпя контроля логических блоков ЦВМ, принцип действия которого .основан на сравнении снгнапов проверяемого и эталонного блоков н которое содержит эталонный блок, схемы сравнения н индикаторы

Наиболее близким техническим решением к данному изобретению является уст ройство дпя контроля логических блоков

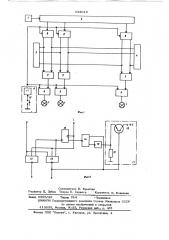

ЦВМ, содержащее генератор импульсов, счетчик, эталонный блок, схемы сравнения, элементы памяти, индикаторы н бпок .управления, причем выход генератора импульсов соединен со входом счетчика, выходы схем сравнения соединены соответственно с первыми входами элементов памяти, вторые входы которых соединены с выходом блока управления, а выходы - с индикаторами

В известных устройствах дпя проверки каждого типа блоков необходимо иметь карты включения коммутационных шнуров, в соответствии с которыми необходимо осуществлять соединения с выхода счетчика проверяемого н этадонного блоков.

Панная процедура существенно усложняет процесс контроля различных типов блоков. !

1епью настоящего изобретенияявляется рашнренне области применения устройства за счет обеспечения возможности контроля различных типов блоков.

Поставленная цель достигается тем, что в устройство введены блоки обнаруженнявходов, первые входы которых соединены соответственно с выходами счетчика, вторые входы - соединены с вылодом блока управления, а выходы соеди ны со входами соответствующих схем сравнения н со входамн н выходами контролируемого н эталонного блоков, а также тем, что блок обнаружения входов содержит триггер, три элемента И-НЕ, элемент

НЕ н эмнттерный повторитель, причем пер6ЗЗО!9

14 ток практически в этом случае отсутствует, то Н8 ее выходе установится низкий уровень, в результате чего после поступления управляющего сигнала с формирователя запуска 11 триггер 16 устано- У вится в состояние, при котором открываются элементы И-НЕ 12 и 13 и тем самым осушествляется подача тестовых комбинаций на данные выводы контролируемого и эталонного блоков. 1Е

В предлагаемом устройстве нет необходимости производить отдельную коммутацию соединений для каждого типа проверяемых блоков. Информация Q том, какой вывод является входом или выходом И контролируемого блока, снимается непосредственно с выводов эталонного блока. Лля перехода на контроль другого типа логических блоков в предлагаемом усч ройстве достаточно лишь заменить эталон- Е ный блок и нет необходимости производить какие-либо дополнительные коммутации.

Кроме того, в предлагаемом устройстве схемы сравнения осуществляют сравне-

ННе не только выходных, но и входных логических уровней, Последнее обстоятельство позволяет обнаружить также такие типы отказов, как электрическое замыкание между входами контролируемого блока.

Формула изобретения

И

1, Устройство для контроля логических блоков ЦВМ, содержащее генератор импульсов, счетчик, эталонный блок, схемы сравнения, элементы памяти, индикаторы и блок управления, причем выход генератора импульсов соединен со входом счетчика, выходы схем сравнения соединены соответственно с первыми входами элементов памяти, вторые входы которых соединены с выходом блока управления, а выходы - с индикаторами, о т л и ч аю ш е е с я тем, что, с целью расширения области применения, в устройство введены блоки обнаружения входов, первые входы которых соединены соответственно с выходами счетчика, вторые входы соединены с выходом блока управления, а выходы соединены со входами соответствуюших схем сравнения и со входами и выходами контролируемого и эталонного блоков.

2. Устройство по и. l, о т л и ч а юш е е с я тем, что блок обнаружения входов содержит триггер, три элемента И-НЕ, элемент НЕ и эмиттерный повторитель, причем первый вход блока соединен с первыми входами первого и второго элементов И-НЕ, второй вход блока соединен со счетным входом триггера и со вторыми входами первого и второго элементов И-НЕ, инверсный выход триггера соединен с третьими входами первого и второго элементов И-НЕ, выходы которых являются выходами блока, выход первого элемента

И-HE соединен с первым входом третьего элемента И-НЕ и со входом эмиттерного повторителя, выход которого соединен через элемент HE со вторым входом третьего элемента И-НЕ, выход третьего элемента И-НЕ соединен с Q- исодом триггера.

633019

+Е

Составитель В. Крылова

Редактор Д. Зубов Техред Е. Гаджега Корректор Н, Ковалева

Заказ 6555/39 Тираж 784: ° Подписное

UHHHflH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4