Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

ОН ИКАНИЕ

ИЗОБРЕТЕНИЯ

< я633133 т.,опз Советеких

Сощиапистичеаки х

Республик

К АВтОРСкаму сииДгЛГльСтвт (51) И" и; р„ ф (6 l) Лополиительное, R 3BT. cBHB""8$ (22) Заявлено 280377 (21 j 2468922/18-09

Н 03 О 3/02

Н 03 К 9/04 е прнеоейииейием заявки №вЂ” (23) ПриоритетГоеудайетвеииыЙ Комитет

Совета Министров СССР но делам иаобретеиий и откры (ий (-Щ Опубликовано15.11.78, Бюллетень № 42 (45) Дата опубликования описания16.1178 (53) УДК621.376.55 (088.8 ) (72) Л вт о о ы изо петенпд

8.Ï.Ëot-.øàêîâ, Л.Б.Гаврилов И-Л.Б.Кривошеев (54) ФАЗОВЫИ ДИСКВИМИНАтор

Изобретение относится к области автоматики< ь .частности к системам автоматического управления.

Известен фазовый дискриминатор содержащий делители частоты входного и апарнага сигналов, выходы разрядов каждого из которых через преобразователи кад-í" ïðÿæ. åíèå сое. двЂ,инены с первымк суммир,ющим и Вычитающим входа ми алгебраического сумматора саответ- 0 ствеина, фильтр нкжних астат, соединенный с выходам алгебраического сумматора, триггер, вклю енный между выходами делителей частоты входного и .опорного сигналов и втарымк суммирую)5 щим и вычитающим входами алгебраического сумматора (Ц .

Однако известный фазавьй дискриминатор обладает значительным дрейфом нуля дискриминационной характеристики, который вызывается изменениями постоянных составляющих напряжений на выходах преабразавателй код-напряжение, в сваю очередь, вызванных неста25 бильностью уровней напряжений, поступающих на входы преобразователей, Цель изобретения — уменьшение дрейфа нуля дискриминационной характерис"

30 тики.

Для этого в предлагаемом фазовом дискриминаторе выходы преобразовате лей код-напряжение входного и опорно=о сигнала ; через дополнительные фильтры нижних частот соединены соответственна с третьими вычитающими и суммирующими вхадамк алгебраического сумматора.

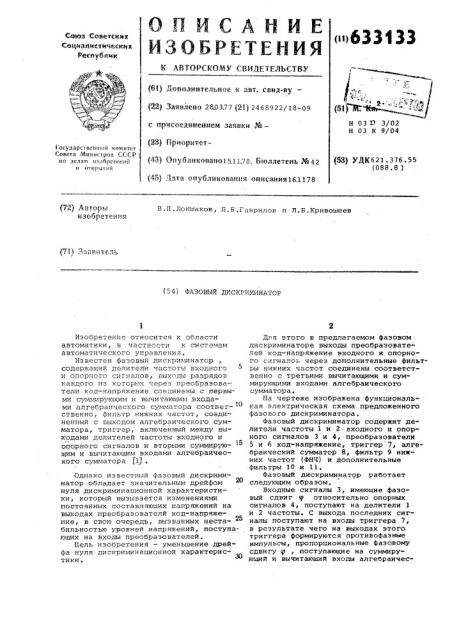

На чертеже изображена функциональная электрическая схема предложенного фазового дискриминатора.

Фазовый дискриминатор содержит делители частоты 1 и 2 входного и опорного сигналов 3 и 4, преобразователи

5 и б код-напряжение, триггер 7, алгебраический сумматор 8, фильтр 9 нижних частот (ФНЧ) и дополнительные фильтры 10 и 11.

Фазовый дискриминатор работает следующим образом.

Входные сигналы 3, имеющие фазовый сдвиг у относительно опорных сигналов 4, поступают на делители 1 и 2 частоты. С выхода последних сигналы поступают на входы триггера 7, в результате чего на выходах этого триггера формируются противафазные импульсы, пропорциональные фазавому сдвигу (p, поступающие на суммирующий и вычитающий входы алгебраичесФормула изобретения

ЦНИИПИ Заказ 6569/45 Тираж 1044 Подписное

Филиал ППП Патент, г.ужгород, ул.Проектная,4

Я 63313 кого сумматора 8. На выходах преобразователей 5 и б код-напряжение формируются ступенчатые импульсы, а на выходах дополнительных фильтров

10 и 11 - сигналы постоянного тока, причем величина сигнала постоянного тока пропорциональна постоянной сос- б тавляющей ступенчатого сигнала на выходе соответствующего преобразова.теля код-напряжевие.

В результате алгебраического суммирования всех сигналов, поступаю- О щий на сумматор 8, Формируется сигнал, постоянная составляющая которого пропорциональна сдвигу фаз (p между входным и опорным сигналами и не зависит от постоянных импульсов, посту- дб пающих с выходов преобразователей 5 и б код-напряжение. Частота пульсаций сигналов на выходе сумматора 8 равна частоте входного (опорного) сигнала. Еа выходе фильтра 9 нижних частот формируется сигнал постоянного тока,.пропорциональный постоянной составляющей сигнала с выхода сумматора 8.

Фазовый дискриминатор уменьшает дрейф нуля дискриминационной характеристики, так как на суммирующий и вычитающий входы алгебраического сумматора 8 поступают сигналы, имеющие взаимно пропорциональные постоянные составляющие, что обеспечивает компенсацию изменения постоянной сос-, тавляющей напряжения на выходе каждого преобразователя код-напряжение И устраняет причину, вызывающую дрейф нуля дискриминационной характеристи- 35 ки.

Дрейф нуля в фазовом дискриминаторе происходит с очень малой скоростью, это позволяет выбрать постоянные времени дополнительных фильтров 40

10 и 11 нижних частот на несколько порядков больше постоянной времени фильтра 9 нижних частот, а следовательно, с выходов дополнительных фильтров 10 и 11 на входы алгебраического сумматора 8 поступают сиг али постоянного тока, которые не иэменяются за время протекания переходных процессов в фазовом дискриминаторе от иэменения сдвига фаз между входным и опорным сигналами, что свидетельствует о сохранении динамической точности.

Таким образом, выходной сигнал фазового дискриминатора пропорционален сдвигу фаз Ч между входным и опорным сигналами, имеет малый дрейф нуля и высокую динамическую точность.

Технико-экономическая эффективность фазового дискриминатора состоит в повышении точности управления при использовании дискриминатора в качестве элемента сравнения в системах автоматического регулирования, в частности в станках с программным управлением.

Фазовый дискриминатор, содержащий делители частоты входного и опорного сигналов, выходы разрядов каждого из которых через преобразователи коднапряжение соединены с первыми суммирующим и вычитающим входами алгебраического сумматора соответственно, фильтр нижних частот, соединенный с выходом алгебраического сумматора, триггер, включенный между выходами делителей частоты входного и опорного сигналов и вторыми суммирующим и вычитающим входами алгебраического сумматора, о т л и ч а ю щ и йс я тем, что, с целью уменьшения дрейфа нуля дискриминационной характеристики, выходы преобразователей код-напряжение входного и опорного сигналов через дополнительные фильтры нижних частот соединены соответственно с третьими вычитающим и суммирующим входами алгебраического сум" матора.

Источники информации, принятые во внимание при экспертизе:

l. Авторское свидетельство СССР

9 311399 ° кл ° B 03 K 7/04с 1970 °