Асинхронное устройство для исправления ошибок

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (61) Дополнительное и авт. свил-ву (22) Заявлено11.12.78 (21) 1978461/18 с присоединением заявки № (23) Приоритет (43) Опубликовано15.11.78.Бюллетень N (45) Дата опубл и кования о и иоанн я 25.1 1

Государстеенный нпмнтет

Совета Мнннстрса СССР пс делам нзобретеннй н PTKpblTNN

26. (72) Автор изобретения

М. Л. Миневич (71) заявитель (54) АСИНХРОННОЕ УСТРОЙСТВО ДЛЯ

ИСПРАВЛЕНИЯ ОйИБОК

Изобретение относится к технике связи и может быть использовано, в частности, для исправления и обнаружения ошибок в информации, поступающей в параллельном виде или хранящейся в устройствах памяти. 5

Известно устройство для исправления ошибок в коде, принимаемом в параллельном коде (1). Оно содержит блок записи информации, буферный регистр, соединенный с блоком записи и с генератором сдвига, декодер для исправления ошибок, соединенный с упомянутым буферным регистром, счетчик числа сдвигов, второй буферный регистр, соединенный с декоде ром, генератор записи, соединенный с декодером и вторым буферным регистром.

Это устройство характеризуется черезмер» ной сложностью и необходимостью осуществления точной синхронизации генераторов сдвига и записи с момента прихода кодового слова. Наиболее близким к изобретению техническим решением является устройство для исправления ошибок в коде

Хэмминга t2 I. Оно содержит декодер, элементы И, элемент ИЛИ, элемент задержки, 3 входов декодера подключены к входам устройства, первые входы элементов И подключены к соответствующим выходам декодера, а выходы соединены с первыми р выходами устройства, первые р входов элемента ИЛИ подключены к входам устройства, вход элемента задержки подключен к первому выходу эле- мента ИЛИ, а выход соединен с (p+ 1) входом декодера. Однако с увеличением кратности исправляемых ошибок быстро растет сложность устройства.

Целью изобретения является повышение достоверности работы. В предлагаемом устройстве это достигается тем, что в него введены два триггера, три дополнительных элемента И, счетчик сдвигов, вход которого подключен к первому выходу элемента ИЛИ, а первый выход соединен со вторыми входами элементов И и о единичным входом первого триггера, нулевые входы триггеров подключены ко второму выходу элементе ИЛИ, единич. ный вход второго триггера подключен к

633149 тить выход q счетчика 5 с выходомЯ. ©

В этом случае схема прекращает работу сразу после Я -ro такта и поступления информации на выход 11.

Таким образом, предлагаемое устройство действительно имеет более широкие фу асциональные возможности, чем известное (обнаруже п е или исправление ошибок любой кратности, выдача информации в параллельном или последовательном коде) и в то же время является более простым, поскольку в нем отсутствукт буферные регистры для преобразования параллельного кода в последовательный и, наоборот, нет схем синхронизации приходящей информации с местными генераторами.

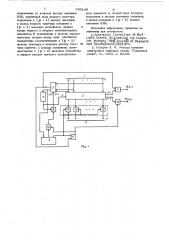

Декодер 2 (мажоритарный) состоит из

11 — каскадного регистра 16 сдвига с г обратной связью, сумматоров 1 7, мажоритарного элемента 18 и выходного сумматора 19 но модулю 2 (см, фиг. 2).

М

При этом сумматоры в соответствии со схемой декодера подсоединены к триггерам регистра 16 сдвига, выходьr. сумматоров подсоединены кз входу мажоритарного элемента 18, выход которого соединен с сумматором 19, на второй вход которого поступают символы из регистра 16.

На каждом такте сдвига с помощью

40 мажоритарного элемента 18 проверяется один символ кодового слова, находящийся в крайней правой ячейке регистра 16, Если в проверяемом символе содержится ошибка, то с выхода мажоритарного элемента 18 снимается сигнал исправления, который суммируется (по модулю 2) с проверяемым символом на сумматоре 19 и по цепи обратной связи вновь записывается на вход регистра 16. $9

3a g тактов оказываются проверенными и при необходимости исправленными все

М символов.

Асинхронное устройство для исправления ошибок, содержащее декодер, элементы И, элемент ИЛИ, элемент задержки, р входов декодера подключены к входам устройства, первые входы элементов И подключены к соответствующим выходам декодера, а выходы соединены с первыми р выходамп устройства, первые р вход элемента ИЛИ подключены к входам, устройства, вход элемента задержки подключен к первому выходу элемента ИЛИ, а иыход соединен с (p + 1) входом декодера, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности работы устройства, оно содержит два триг» гера, три дополнительных элемента И, счетчик сдвигов, вход которого подключен к первому выходу элемента ИЛИ, а первый выход соединен со вторыми входами элементов И и с единичным входом первого триггера, нулевые входы триггеров открытъ и элемент И 1 2 закрывает элемент

И 8. Тем самым запрещается прохождение (Я + A )-го импульса с выхода элемента 4 через элемент И 8 на вход элемен» та ИЛИ 3, и тактовые импульсы прекращают поступать на вход 9 декодера 2. г

Если, например, требуется получение информации на выходе только в параллельном коде, то для этого достаточно совмесТаким образом, в этом частном случае число тактов декодирования Ц раино числу символов r1 . Поэтому выход счетчика

5, соответствующий t1 -му импульсу, соединен с триггером 6 и элементом И

12.

Счетчик 5 считает до и, затем автоматически сбрасывается à 0", одновременно записывает 1 в триггер 6 и подает сигнал на элементы И 10 для считывания информации в параллельном коде. Потенциал с триггера 6 открывает элементы

И 12 и 14, и декодированная информация, через элемент И 14 поступает в последовательном коде на выход. За g тактов вся информация считывается на выход, очередной сигнал со счетчика 5 проходит через элемент И 12 на элемент И 8, и поступление импульсов сдвига прекращается. Схема готова к декодированию следуюшего кодового слова, Триггер 7 подсоединен свопм единичным входом к выходу мажоритарного элемента l B, поэтому любое исправление переводит триггер 7 в состояние "1, что свидет.льствует о наличии ошибки в принятом кодовом слове.

Предлагаемое устройство, по сравне п ю с известным, позволяет существенно повысить достоверность и надежность приема информации. Положительный эффект от использоваш я предлагаемого устройства существенным образом зависит от значимости и це ности передаваемой информации. В системах связи использование этого устройства приводит как к увеличе нию скорости передачи информации при заданной достоверности, так и к уменьше ник, занятости канала связи.

Фîpмy:ла изобрeòåíèÿ

633149

ФЫ 2

Составитель Т. Бондаренко

Редактор Л. Тюрина Техрбд 3. Фанта Корректор М. Демчик I ° I

Заказ 6571/46 Тираж 763 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4