Устройство для сложения чисел

Иллюстрации

Показать всеРеферат

тисксо чтт те тя (!!! 634274

Союз Советских

Социалистических

Реслублик (61) Дополнительное к авт. свид-ву (22) Заявлено18.03.76 (21) 2336381/18-24 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано 25.11 78 Бюллетень № 43 2 (51) М. Кл.

Cj 06 Р 7/385

Государстеенни!й комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК 681.325 (088.8) (45) Дата опубликования описания 23,И .78 j (72) Авторы изобретения

В. И. Кабин, В, И, Корнейчук, В, B. Макаров и В. П. Тарасенко

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ

Изобретение относится к области вычислительной техники и может быть применено в цифровых вычислительных машинах и устройствах, построенных на основе больших интегральных схем.

Известны устройства сложения (1), оперирующие с числами, представленными в позиционной системе счисления. Однако с помощью таких устройств нельзя совмещать во времени процесс поразрядного ввода слагаемых со старших разрядов с процессом формирования цифр результата. Это приводит к увеличению времени получения кода результата при последовательном поступлении очередных разрядов слагаемых, особенно если период их поступления ограничен внешними по отношению к устройству факторами (например, быстродействием источников информации).

Наиболее близким техническим решением к настоящему является устройство для сложения чисел, содержащее элементы И, выходной регистр, сумматор, выходы млад- 2Ц ших разрядов которого подключены ко входам выходного регистра, выходы которого подключены к соответствующим входам сумматора, выходы двух старших разрядов которого соединень! с выходными шинами устройства через элементы И, другие входы которых подключены к первой управляющей шине устройства (2) . Зто устройство позволяет совмещать во времени процессы поразрядного ввода o!:ерандов и формирования результата, однако при одновременном сложении !

l cJxo,!ь|;!!х:Il!cL быс родействие 3Tol о устрой! гза !!е!1е, I!!!;о.

Цег!ь!о настоящего изобретения является увели!е!!!!е быстродсйствия.

Поставг!ен!!ая цель достигается тем, что устройство содержит шифраторы, выходы которых подключены к соответствующим входа сумматора. и функциональные регистры, выходы которых подключены ко входам соответствующих и!пфраторов, B oäû функциональных регистров соединены с соответствующими информац!!онными шинами устройства, а управляющие входы функциоkIà lbkibIi; рсг!!строй подключены ко второй и третьей управляющ:;; шинам устройства, четвсрт;!л у!!равляющая шина устройства соединена с управляюпгпм входом выходного ре! ис! ра, !!р!! !ем функциональные регистры содержат элементы запрета, элементы И, элементы И,1И и триггеры, причем )-е ин6342 74

3 формационные входы (i = 1, ..., k) функLlèîHÿëüHûx регистров через j-е элементы И первой группы подключены ко входа,t установки в единице„ -х триггеров и через элементы запрета — ко входам уста IoBKH в нуль j-x триггеров, а вторые входы всех элементов запрета и элементов И первой группы подключены к первому управляющему входу функционального регистра, второй управляющий вход которого подключен к первым входам каждого j-ro элемента И второй группы, выходы которых через j-e элементы ИЛИ подключены к тактиру .ощим входам j-х триггеров и через (—

j — 1)-е элем нты ИЛИ вЂ” к тактирующим входам (i — 1)-х триггеров, едичичные выходы которых подключены к информационным входам j-х триггеров, единичные выходы которых соединены с первыми входами j-x элемечтов И третьей группы, выходы которых являются выходами j-х разрядов функционального регистра, а вторые входы j-x элементов И третьей группы соединены с нулевыми выходами (j — 1)х триггеров и со вторыми входами() — (-х элементов И второй группы.

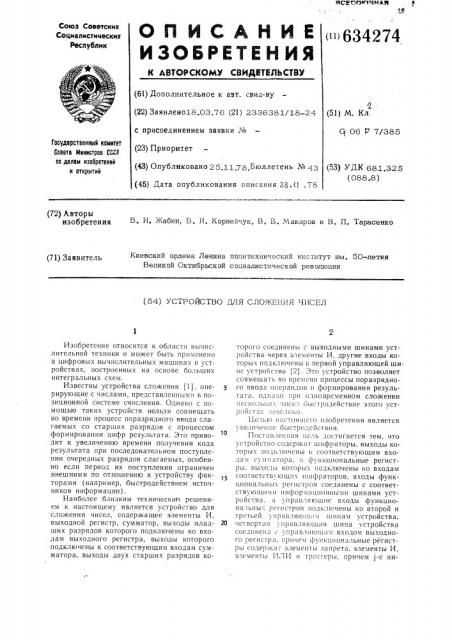

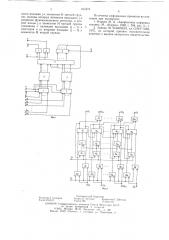

Иа фиг. 1 изображена структурная схема устройства для сложения чисел; на фиг. 2 — схема функционального регистра.

Устройство содержит функционал ьнь1е ре гистры 1, 2, шифраторы 3, 4, сумматор 5 и выходной регистр 6. Выходы функциональных регистров 1, 2 подключены состветственно ко входам шифр-торов 3, 4. Ко входам разрядов сумматора 5, имеющим вес 2", подключены выходы разрядов шифратора 3 к

1 выходного регистра 6, имеющие вес 2, и выходы разрядов шифратора 4 с весом 2 .

Выходы младших разрядов сумматора 5 подключены ко входам выходного регистра 6.

В состав устройства также входят элементы

И 7, 8, информационные входы 9i — 9, (ф = k количество слагаемых), управляющие входы !Π—: 11, 12, выходы 13, 14, управляющий вход 15, первые входы элементов И 7, 8 связаны с выходами двух старших разрядов сумматора 5. Информационные входы 9i, 94, 9; ... 9,„, подключены ко входам функционального регистра 1, а информационные входы 94, 9л, ... 9„подключены ко входам функционального регистра 2.

Управляющий вход 10 связан с управляющим входом приема кода функциональных регистров 1, 2. Управляющий вход 11 подключен к управляющим входам сдвига кода функциональных регистров 1, 2. Вторые входы элементов И 7, 8 подключены к управляющему входу 12, а выходы элементов

И 7, 8 соединены с выходами устройства 14, 13. Управляющий ".:i выходного регистра 6 соединен с управ, яющгм входом 15. Выходной регистр 6 и су ма: р 5 содержат соответственно по ) In; m 4 )2+ 1одрт(двоичных разрядов, а ф ниональные регистры 1, 2 — по k = ф двоп ных разрядов. В состав каждого функционального регистра

1 и 2 входят (см. фиг. 2) триггеры 16i — 16„, элементы ИЛИ 17i — 17,. и элементы И

18i — 10„, Триггеры 16i — 16, могут быть построены по схеме D-триггеров с внутреннеи задержкой. Тактирующие входы три ггеров

16i — 16„., соединены с выходами элементов

ИЛИ 17, — 17„„. Входы каждого элемента

ИЛИ 17j (j = 1, k — ) соединены с выходами элементов И 18, и 18„н . Инверсные

10 выходы триггеров 16j подключены к первым входам элементов И 18,, а единичные выходы каждого триггера 16, подведены к информационным входам триггеров 16 „1. Г1ричем информационный вход триггера 16 подключен к генератору логического нуля (на15 пример, к земле). Функциональные регистры содержат также элементы И 19i — 19„, элементы запрета 20, — 20, элементы

И 21, — 2!к ь управляюший вход 22, информационные входы 23 — 23„, управляющий вход 24 и выходы 25 — 25„. Единичный выход триггера 16i подключен к выходу 25к, а к остальным выходам 25 — 25, подключены соответственно выходы элементов

И 21Ä,— 21, . Один вход каждого эле мента

И 21, (j = 1, k — 1) подключен к нулевому

25 выходу триггера 16,, а второй — к единичному выходу триггера 16,,1 . Информационные входы 23 — 23, соответственно через элементы И 19 — 19к и элементы запрета

20 — 20к подключены ко входам установки в единицу и ко входам установки в нуль

30 триггеров 16; — 16„. Ко вторым входам элементов Л 19i — 19 и элементов запрета

20; — 20„подключен управляющий вход 22, а управляющий вход 24 подведен ко вторым входам элементов И 18i — !А.

Устройство работает следующим образом.

В исходном состоянии в функциональных регистрах 1, 2 и в выходном регистре 6 записаны нули в каждом разряде. К началу каждого i-го цикла работы на входы 9i — 9 поступают i-e цифры операндов, представ40 ленных в избыточной двоичной системе счисления с цифрами (О, 1,2). Операнды, общее количество которых равно k, поступают в устройство, начиная со старших разрядов.

Значение очередного разряда каждого $-го

45 операнда (ь = 1, k) кодируется сигналами на входах 9 e-> и 9 е. Цифре 2 соответствует единичный сигнал на входах 9 е-t a цифре 1 — на входах 9ее. Отсутствие единичных сигналов на шинах 9ее 1 и 9 е соответствует цифре E-го операнда, равной О.

В первом такте каждого i-го цикла работы по управляющему сигналу, поступающему на управляющий вход 10, в функциональные регистры 1 и 2 заносится код, определяемый значениями сигналов, поступающих на

55 информационные входы 9i — 9 . Если при этом (см. фиг. 2) на вход 23j функционального регистра поступит нулевой сигнал, то с выхода элемента запрета 20 единичный сигнал установит триггер 16„в «О.>. Если на вход 23, носгупаег единичный сигнал, 1о с

634274

Фор яула изобретения

) выхода элемента И 19 единичный сигнал установит триггер 16 в «1». Затем на управляющий вход 11 поступает серия из k — 1сигналов, осуществляющих сдви" информации.в функциональном регистре 1 и 2. Если в триггере 16„записана «1», то состояние триггеров 16; t и 16, при постуглении сигнала на вход 24 не изменяется, так как элемент И 18 закрыт нулевым сигналом с выхода триггера 16„ . Если же в триггере 16, записана цифра «0», то при поступлении сигнала на вход 24 срабать.вгет элемент

И 18„, так как на нулевом выходе триггера

16, в этом случае присутствует единичный сигнал. В результате этого через элемент

ИЛИ 17; на тактирующий вход триггера

16; поступает единичный сигнал, ссуществля. ющий перепись информации кз триггера

16 > -i в триггер 16,. После поступления k — 1 управляющих сигналов на вход 11 в фч.нкциональных регистрах сказывается сформированным код, все единицы в котором располагаются подряд в младших разряда.;. Например, если первоначально в функциональном регистре 1 или 2 был записан код

101100011, то после функционального сдвига будет получен код 000011111. На выходах функциональных регистров 1 и 2 образуется код, значение j ãî разряда которого равно единице, а значения остальных разрядов равны нулю, где j — суммарное количество единиц, поступивших в регистры. Например, если в функциональном регистре 1 или

2 записан код 000011111, то на выходах

25 — 25„будет присутствовать код 000010000.

Единичный сигнал с выхода каждого функционального регистра 1 и 2 выбирает j iî входную шину соответственно шифраторов

3 и 4, на выходах которых формируются двоичные коды чисел ). Например, для приведенного выше кода на выходе функционального регистра ) = 5. Следовательно, на выходе соответствующего шифратора будет сформирован код 0101. В сумматоре 5 формируется код

А + 2А + 2А,, где Ai — значение кода с выходов шифратора 4; A> — значение кода с выходов шифратора 3; А, — значение кода, записанного в выходном регистре 6. По управляющему сигналу, поступающему на угравляющий вход 12, осуществляется выдача информации с выходов двух старших разрядов сумматора 5 на выходы устройства 13 и 14 через элементы И 7 и 8. Наличие единичного сигнала на выходе 13 соответствует очередной цифре результата, равной 2, на выходе 14— цифре результата, равной 1, а отсутствие единичных сигналов на выходах 13 и 14 означает, что очередная цифра результата равна О. По управляющему сигналу, поступающему на управляющий вход 15, производится прием кода младших разрядов сумматора 5 на выходной регистр 6. На этом заканчивается один цикл вычисления. В каждом i-м цикле на входы устройства поступа5

40 ют очередные разря;ы опесандов с весом

2 и формируется очередной вазряд результата, и.»cþ öèè вес 2 = . 11роцесс

; +)Pop (l вычисления заканчивается после получения требуемого числа разрядов результата. Для получения всех значащих разрядов результата необходимо выполни« ь п + j1og> >k(+ 1 циклов вь! чксленкя.

Время выполнения одного цикла вычисления определяется в основном длительностью выполнения одной микрооперации суммирования и l — 1 микроопераций сдвига. Таким образом, за счет введения дополнительного состава аппаратуры увеличено быстродействие устройства прп одновременном сложении нескольких чисел.

Устройство для сложения чисел, содержащее элементы И, выходной регистр, сумматор, выходы младших разрядов которого подключены ко входам выходного регистра, выходы которого подключены к соответствующим входам сумматора, выходы двух старшкх разрядов котопого соединены с выходными шинами устройства через элементы И, другие входы которых подключены к первой управляющей шине устройства, отличающееся тем, что, с целью увеличения быстродействия при сложении ческольких чисел, оно содержит шифраторы, выходы которых подключены к соответствующим входам сумматора, и функциональные регистры, выходы которых подключены ко входам соответствующих шифраторов, входы функциональных регистров соединены с соответствующими информационными шинами устройства, а управляющие входы функциональных регистров подключены ко второй и третьей управляющим шинам устройства, четвертая управляющая шина устройства соединена с управляющим входом выходного регистра, причем функциональные регистры содержат элементы запрета, элементы И, элементы

ИЛИ и триггеры, vðè÷åì !-е информационные входы (.1 = 1, ..., k) функциональных регистров через j-e элементы И первой группы подключены ко входам установки в «единицу» )-х триггеров и через элементы запрета — ко входам установки в «нуль» 1-х триггеров, а вторые входы всех элементов запрета и элементов И первой группы подключены к первому )правляющему входу функционального регистра, второй управляющий вход котсссго подключен к первым входам каждого j-го элемента И второй группы, выходы которь,х через j-е элемечты ИЛИ подключены к тактирующим входам j-x триггеров и через (j — 1) -е элементы ИЛИ— и тактирующим входа" » (j — i)-х триггеров, единичные выходы которых подключены к информационным входам 1-х триггеров, единичные выходы которых соединены с пер634274

Фига

Составитель В. Березкин

Редактор А. Садомов Текред О. Луговая Корректор С. Шекмар

Заказ 6763, 47 Тираж 784 Подписное

ЦНИИПИ Государственного комитета Совета Министров CCCP по делам изобретений и открья нй

113035, Москва, Ж-35, Рву инская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул Проектная, 4 выми входами j õ элементов И третьей группы, выходы которых являются выходами 1-х разрядов функционального регистра, а вторые входы j õ элементов И третьей группы соединены с нулевыми выходами (j — 1) -x триггеров и со вторыми входами (j — 1)-х элементов И второй группы.

Источники информации, принятые во внимание при экспертизе:

1. Карцев М. А. «Арифметика цифровых машин», М., «Наука», 1969, с. 294, рис. 3 — 1.

2. Заявка № 2104692/24, кл. G06 F 7/385, 1975, по которой принято положительное решение о выдаче авторского свидетельства.