Устройство для проведения статистических испытаний

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических е еспублик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

634288

К ЬВтОРСКОМ СВИДЕПЛЬСтВЮ (61) Дополнительное к авт. свил-ву (22) Заявлено 14.04.7 5 (21) 2123052/18-24 с присоединением заявки % (23) Приоритет (43) Опубликовано 5.11.78.Бюллетень № 3 (45) Дата опубликования описания 28.11.78

Z (51) M. Кл

Я 06 F 15/36

Госудерстеенний комитет

Совете Министрое CCCD по делам изобретений и открытий (53) УДК 681,325 (088. 8) (72) Автор изобретения

Ю. Б. Виленкин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРОВЕДЕНИЯ

СТАТИСТИЧЕСКИХ ИСПЫТАНИЙ

Изобретение относится к вычислитель. ной технике и предназначено для измерения характеристик случайных явлений.

Оно может быть использовано при проведении испытаний надежности аппаратуры, в ядерной физике и других областях 5 науки и техники.

Известно устройство для проведения статистических испытаний, содержащее триггеры предварительного хранения, 10 счетчики-делители частоты, коммутаторы, блок оперативной памяти (1)

Недостатком этого устройства является большой объем оборудования на каж-дый канал счета и, соответственно, высокая стоимость.

При построении устройств на сотни и тысячи каналов счета стремятся найти более экономичные решения путем разделения, с одной стороны, функции счета, а с другой, запоминания и вывода резул татов между счетчиком и блоком оперативной памяти.

2.

Из известных устройств наиболее близким по технической сущности к изобретению является устройство, которое содержит группу триггеров, информационные вхоQbJ которых соединены с информационным входом устройства, выходы подключены к соответствующим входам коммутатора, счетчик, соединенный двусторонними связями с блоком памяти, и счетчик адреса 2)

Недостатком устройства является относительно малая частота счета по каналам, так как количество импульсов, которое может быть сосчитано по каждому каналу в единицу времени, определяется формулой где . — время обращения к блоку памяти;

М вЂ” количество каналов.

Белью изобретения является повышение быстродействия устройства.

634288

Поставленная цель достигается тем, что в устройство введены дополнительные группы триггеров, коммутаторы, счетчики, элементы запоминания переполнений, элементы И, НЕ, первый дешифратор, соединенный с группой млацших разрядов счетчика адреса, второй дешифратор, соединенный с группой старших разрядов счетчика адреса и переключатель, причем информационные входы триггеров каждой щ дополнительной группы соединены с соответствующим информационным входом устройства, выхоцы подключены к вхоцам соответствующего коммутатора, а счетчики соединены: двусторонними связями с 5 блоком памяти, управляющие входы каждого коммутатора и триггеров каждой группы подсоединены к выходу первого дешифратора, выход старшего разряда каждого из счетчиков через соответствующий 2ф элемент запоминания переполнений соединен с первым вхоцом соответствующего первого элемента И, второй вход которого через последовательно соединенные элемент НЕ и переключатель соединен с вь - 5 ходом второго цешифратора, счетный вход каждого счетчика поцключен к выходам соответствующих первого и второго элементов И, первые входы вторых элементов

И соединены с выхоцом второго цешифра- 3у тора, выход каждого коммутатора подключен ко второму входу соответствующего второго элемента И.

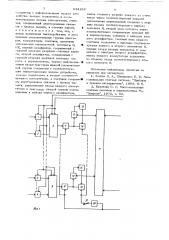

Схема устройства представлена на фиг.1и2, 35

Источники импульсных сигналов соединены с триггерами 1, 2, 3, 4 нескольких групп, которые соединены с коммутаторами 5, 6, Выходы коммутаторов 5 6 соединены со входами элементов И 7, 8, 46 выходы которых соединены со счетными входами счетчиков 9, 10. Входы и выходы разрядов счетчиков соединены с соот/ ветствуюшими . выходами и входами разрядов блока 11 памяти. Выходы старшего: 45 разряда счетчиков 9, 10 соединены с элементами запоминания переполнений

12, 13, которые соединены со входами элементов И 14, 15, выходы которых соединены со счетными входами счет- 5О чиков 9, 10.

Входы младших и старших разряцов адреса блока памяти соединены соответственно с выходами разрядов счетчика адреса (на схеме счетчик адреса показаи 55 в виде двух счетчиков 16 и 17.).

Выходы разрядов счетчиков 16 и 17 соединены также с дешифраторами 18 и

19, Счетный вход и выход переполнения счетчика 16 через переключатель 20 соединены со счет ым входом счетчика 21, имеющего то же число разрядов, что н счет чик 16. В режиме счета переключа-тель 20 соединяет выход переполнения счетчика 16 со счетным входом счетчика 21, а в режиме вывода результатов счета переключатель 20 соединяет счетные входы счетчиков 16 и 21> выходы разрядов которых соецинены со схемами сравнения 22, 23, 24, Схема сравнения

23 имеет вход разрешения от схемы сравнения 22; а схема сравнения 24 имеет вход разрешения от схемы сравнения 23.

Прямые и инвертированные выходы схем 22, 23, 24 соединены с соответсч вуюшими парами элементов И 25 и 26, 27 и 28, 29 и 30, другие входы которых соединены с несколькими выходами цешифратора 19, соответствующими первым по порядку состояниям счетчика 17, Ос тальные выходы дешифратора 19, кроме выхода, соответствующего последнему состоянию счетчика 17, соединены с элементом ИЛИ 31, который через элемент

И 32, второй вхоц которого соединен с генератором тактовых импульсов (ГТИ)

33 соединен со счетным входом счетчика 17. Входы элемента ИЛИ 31 соединены также с выходами элементов И 26, 28, 30. Выхоцы элементов И 25, 27, 29 и последний выхоц дешифратора 19 соединены с элементом ИЛИ 34, который через эльмент И 35, второй вход которого соединен с генератором 33, соединен со сче лным входом счетчика 16 и входом сброса счетчика 17, Выхоц дешифратора 19 соединен со входами элементов И 7, 8 и элементом HE 36, который через переключатель 37 соединен со входами элементов И 14, 15. Переключатель 37 замкнут в режиме счета и разомкнут в режиме вывода его результатов.

Устройство цля проведения статистических испытаний работает следующим образом, В каждом тактовом интервале генератора 33 происходит обращение к слову блока 11 памяти, считывание из него кодов в счетчики 9, 10, выработка в них новых кодов и запись их в выбранное слово блока 11 памяти. При сброшенном состоянии счетчика 17 происходит обращение к последовательным словам первого массива слов. При этом цешифратор 18 обеспечивает подключение через коммутаторы 5, 6 к элементам И 7, 8 соответствующих триггеров из 1, 2, 3, 634288

4, Если эти триггеры находятся в единичном состоянии, то есть, если зя интервал разрешения системы ня них поступили импульсы приращения, то в соответствующие счетчики из 9, 1 О поступают у счетные и .. пульсы.

Если после обращения к очередному слову первого массива не имеет место совпадение кодов, поступаюших ня схему сравнения 22, то включается элемент И М

25, элемент ИЛИ 34 и очередной тактовый импульс проходит через элемент

И 35 на счетный вход счетчика 16 и на вход сброса счетчика 17. После этого происходит обращение к следующему сло- И ву первого массива и опрос следуюших три гг еров.

Если имеет место совпадение кодов, поступающих на схему 22, то включается элемент И 26, элемент ИЛИ 31 и элемент И 32 пропускает очередной тактовый импульс на счетный вход счетчика

17, а состояние счетчика 16 зя тактовый интервал не изменяется..Счетчик 17 вььходит из первого состояния и разрешающий сигнал снимается с элементов И

7, 8 и через элемент HE 36 подается на элементы И 14, 15. В следующем тактовом интервале происходит обращение к слову второго массива с тем же поряд-® ковым номером в массиве.. К кодам, хранящимся в этом слове, добавляются сигналы переноса, хранящиеся в элементах запоминания переполнений 12, 13.

Если в тактовом интервале, в котором происходит обращение к слову второго массива, имеет место совпадение кодов, поступаюших на схемы 22 и 23, то в конце тактового интервала происходит добавление 1 в счетчик 17 и в следуюшем тактовом интервале происходит обращение к тому же номеру слова третьего мас сива.

Если в такте обрешения к слову второго массива совпадение на обеих схемах

22 и 23 не будет иметь место, то произойдет добавление 1" в счетчик 16, сброс счетчика 17, опрос следующей группы триггеров и обращение к следуюшему слову первого массива.

Если при обращении к слову третьего массива имеет место совпадение на схемах 22, 23, 24, то в следующем такте произойдет обрашение к слову четвертого массива с тем же порядковым номером в нем.

Если при обрашении к слову третьего массива совпадение на схемах 22, 23, 24 н е им еет место, то в конце такта происходит сброс счетчика

17 и добавление "1" в счетчик 16, опрос следуюшей группы входных квкелов и обращение к соответствующему слову первого массива.

После обряшения к слову четвертого массиве благодаря соединению соответству-; ющих номеров выходов дешифреторе 19 с элементом ИЛИ 31, происходит добавление

"1 в счетчик 17. При достижении счетчиком 17 последнего состояния благодаря соединению последнего выходя дешифраторя 19 с элементом ИЛИ 34 происходит сброс счетчика 17 и добавление 1" в счетчик 16, после чего в следуюшем тякТр произойдет обращение к следующему номеру слова первого массиве.

После окончания цикла обращений ко всем словам первого массиве сигнал переполнения со счетчике 16 добавляет 1 " в счетчик 21, и начинается новый цикл опросе входных коммутаторов н обряшений к словам первого массиве, в котором аналогичным образом происходит обрашение к словам других массивов, Описанное построение устройства обеоцечивяет то, что каналы счете образукл оя одноименными разрядами всех массивов.

При выводе результатов счета последовательно опряшивяются одинаковые номера слов всех-массивов, в результате чего выводятся результаты счете, по rn канелем, После этого номер опрашиваемых слов в массивах увеличивается на 1 и т,д, до выьодя результатов счета по всем канелем. Такой режим работы устройстве обеспечивается тем, что из-зе соединения при выводе результатов счетных входов счетчиков 16 и 21 их коды всегда совпадают. Поэтому после опроса слове пер вого массива опрешиваются слова с тем же номером в других массивах.

При опросе последнего массива благодаря включению элемента И 35 от дешифратора 19 происходит добавление «I в счетчике 16 и 21, зятем обеспечивается последовательный опрос слов массивов с новым номером в этих мяссивеХ. Так кек в режиме выводе элементы И 14, 15 отключены, то накопленные результаты при выводе не изменяются.

Формула изобретения

Устройство для проведения статистических испытаний, содержашее группу триггеров, информационные входы которых

634288 соединены с информа IHoHHblM входом уст õ>Àcõåå, выходи подключены и соответствующим входам коммутатора, счет чик, соединенный двусторонними связями с блоком памяти, и счетчик адреса, М о т л и ч а ю щ е е с я тем, что, с нелью повышения быстродействия, в него введены дополнительные группы триггеров, коммутаторы, счетчики, элементы запоминания переполнений, элементы И, ©

Н Е, первый дешифратор, соединенный с группой младших разрядов счетчика адреса, второй дешифратор, соединенный с группой старших разрядов счетчика адреса, и переключатель, причем информаци — И онные входы триггеров каждой дополнительной группы соединены с соответствукщим информационным входом устройства, выходы подключены к входам соответствующего коммутатора, а счетчики соединь-М ны двусторонними связями с блоком памяти, управляющие входы каждого коммутатора и триггеров каждой группы подсоединены к выходу первого дещифратора, выход старшего разряда каждого v. счетчиков через соответствующий элемент запоминания переполнений соединен с первым входом соответствующего первого элемента И, второй вход которого через последовательно соединенные элемент HE и переключатель соединен с выходом второго дешифратора, счетный вход каждого счетчика подключен к выходам соответствующих первого и второго элементов И, первые входы вторых элементов И соединены с выходом второго дешифратора, выход каждого коммутатора подключен ко второму входу соответствующего второго элемента И.

Источники информации, принятые во внимание при экспертизе:

1, Злобин И. А„Шепаренко E. E. Многоканальная счетная система. Приборы и техника эксперимента", 1968, № 6, 2, Курочкин С. С. Многоканальные счетные системы и коррелометры. M., "Энергия, 1972, с. 82.

634288

Риг Д

Составитель А. Жеренов

Редактор А, Садомов Техред Н. Андрейчук Корректор. Л. Небола

Заказ 6764/48 Тираж 784 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открь;тий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4