Устройство для контроля электрического монтажа

Иллюстрации

Показать всеРеферат

(ii)634291

Союз Советских

Социалистимеских

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К AB ÎÐÑÊÎÌÓ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено05.05.76 (21) 2355685/18-24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано25.11.78.Бюллетень № 43

9 (51) М. Кл.

С 06 Р 15/46

Cj 01 R 31/02

Гасударственный квинтет

Савета Министрав СССР ао делам изабретений и открытий (53) УДК 621.317.

° 7 9 1(088.8) (45) Дата опубликования описания 23 ° И .78 (72) Авторы изобретения

А, М. Караваев и А. И. Ярин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО

МОНТАЖА

Изобретение относится к области вычислительной техники и может быть использовано для контроля электрического монтаж.-. различных электронных устройств.

Известны устройства (1), содержащие измерительный блок, коммутаторы опроса,блок считывания, блок памяти, блок комму5 тационных ключей.

Недостатком известных устройств является их сложность.

Наиболее близким к данному по сущности технического решения является устройст- ð во (2), содержащее дешифратор, логические ячейки памяти, узел считывания; узел индикации, узел синхронизации, узел анализа, два входных регистра и элемент ИЛИ, причем каждый выход дешифратора подклю. чен к первому входу соответствующей логической ячейки памяти, первый выход которой соедичен с соответствующим выходом устройства, первый вход узла анализа соединен с выходом элемента ИЛИ, входы которого соединены со вторыми выходами соответству- 2О ющих логических ячеек памяти, входы onроса которых соединены соответствен но с выходами опроса узла анализа, выход узла считывания подключен ко входам первого и второго входных регистров, второму входу узла анализа и первым входам узла синхронизации и узла индикации, второй выход узла анализа подключен ко вторым входам узла индикации и узла синхронизации, первый выход которого соединен со входом узла считывания, третий вход и второй выход узла синхронизации соединен соответственно со вторым выходом и третьим входом узла анализа.

Основным недостатком известного устройства является сложность выявления лишних и неверных соединений из-за отсутствия.возможности автоматического поиска указанных неисправностей. Кроме того, в случае выхода из строя ячейки памяти (нет записи

«1»), устройство выдает «ложный» сигнал наличия цепи.

Целью настоящего изобретения является расширение функциональных возможностей устройства, повышение достоверности контроля.

Поставленная цель достигается тем, что в устройстве введены узел переключения, регистр текущего адреса и схема сравнения адресов, причем третий и четвертый выходы узла анализа подключены соответствен634291

35 о

55 но ко входу регистра текущего адреса и первому входу узла переключения, выход которого соединен со входом дешифратора, входы схемы сравнения адресов подключены к выходу второго входного регистра и первому выходу регистра текущего адреса, второй вход которого и выход первого входного регистра подключены соответственно ко второму и третьему входам узла переключения, выход схемы сравнения адресов соединен с четвертыvl входом узла анализа.

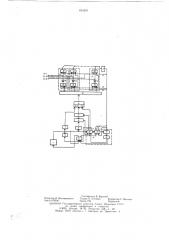

На чертеже представлена блок-схема устройства для контроля электрического монтажа, которое содержит узел считывания 1, узел 2 индикации, узел 3 синхронизации, узел 4 переключения, регистр 5 текущего адреса, схема 6 сравнения адресов, первый

7 и второй 8 входные регистры, узел 9 анализа, дешифратор 10, элемент ИЛИ 11, логическую ячейку 12 памяти, входы устройства 13 — 1 — 13 — -и. В состав логической ячейки 12 памяти входят, например, диод 14, триггер 15 и элемент И 16. В состав узла 9 анализа входят, например, сдвиговый регистр 17, дешифратор 18, формирователь 19 управления сигналов и распределитель 20.

На чертеже обозначены входы опроса 21, 22 и 23.

Устройство работает следующим образом.

По команде узла 3 синхронизации формирователь 19 подключает входной регистр

7 к дешифратору !О, а распределитель 20 по входу 23 записывает «1» в триггеры всех логических ячеек 12. Г1ри подключении входного регистра 7 на одном из выходов дешифратора 10, номер которого определяется числом, записанным B регистре 7. появляется сигнал и соответствующая логическая ячейка готовится к считыванию. Импульс считывания поступает на вход 21 с распределителя 20. Поскольку на первом и втором входах элемента И 16 присутствуют сигналы с выхода триггера 15 и дешифратора 10, то на выходе данной ячейки появится импуль, который через элемент ИЛИ 11 поступит на входы распределителя 20 и сдвигового регистра 17. Сдвиговый регистр 17 производит запоминание считанной «1», а распределитель 20 по входу 22 производит запись «0» в триггер 15 выбранной логической ячейки

l2. На выходе триггера 15 появится нулевой сигнал, который поступит на элемент И 16 данной ячейки и на соответствующий вход

13, например 13- 1. Если данная точка имеет соединение с другими точками, то потенциал «О» поступит на элемент И 16 ячеек, которые соединены с этими точками.

После опроса первого адреса формирователь 19 подключает к дешифратору 10 регистр текущего адреса 5, а распределитель

20 производит считывание информации из логической ячейки 12, номер которой соответствует числх, записанному в регистре текугцего адреса 5. Если эта точка, например

13 — 2, имеет гальваническую связь с исходной точкой 13 в 1, то произойдет считывание

«О», т. к. элемент И 16 логической ячейки 12 будет закрыт потенциалом «О», поступаюгцим через соединение в монтаже и вход

13 — 2. Если точка 13 — 2 не имеет гальвани- ческой связи с точкой 13 — 1, то произойдет с гитывание «1», так как элемент К1ббудет открыт единичными сигналами с выхода триггера 15 этой ячейки и соответствующего выхода дешифратора 10.

Таким образом, с выхода элемента ИЛИ

11 при проверке соединения между двумя точками снимается код «10» при наличии соединения между точками или «ll» — при отсутствии соединения между точками.

Для повышения достоверности контроля устройство производит вторичный опрос тех же адресов, который производится по описанному выше алгоритму, но адреса опрашиваются в обратной последовательности.

После вторичного опроса сдвиговый регистр 17 будет хранить код «10, 10» — при наличии соединения, код «11, 11» — при отсутствии соединения.

Формирователь 19 но сигнала 1 дешифратора 18 и схемы сравнения адресов 6 выдаст на узел 3 синхронизации сигналы для организации проверки новой пары адресов или считывания нового кода информации, а. также сигнал формирования текушего адреса в регистр текущего адреса 5.

Неисправность триггеров 15, элементов И

l6 и ИЛИ 1 или случайный сбой приводит к изменению выходного кода выдаваемого

và вход узла анализа. Так, например, отсутствие прохождения сигнала через элемент И 16 в какой-либо логической ячейке памяти 12 приводит к появлению кода

«0110» или «1001» при проверке соединения между точкой, соответствующей этой ячейки, и любой другой. Дешифратор 18 выявляет все возможные изменения кода, возникшие при неисправности логических ячеек или слуьчайном сбое, и выдает сигнал на узел

3 синхронизации для повторной проверки соединения между теми ?Kc точками.

Если при вторичной проверке происходит изменение кода, то происходит останов устройства.

В режиме самоконтроля, при исправных логических ячейках 12, в узел анализа поступают код «10» при наличии соединения и код «11» при отсутствии соединения цри прямом и инверсном опросах. Соответственно могут выделяться неисправности устройства, искажающие заданные реакции на определенные воздействия.

Х стройство позволяет также контролировать блоки, построенные на базе логически. . элементов И, ИЛИ, НЕ

Программа проверки подобного логического блока наносится на программоноситель, например перфоленту.

63429!

Формула изобретен((я

В начале записывается кадр, которь(й содержит признак начала проверки, за ним кадры, каждый из которых содержит адрес входной точки проверяемого блока, признак

«О» («!»), который нужно подать на этот вход, и команду записи информации. Далее записываются кадры, которые содержат адреса выходных точек проверяемого блока, признаки «О» или «1», которые должны поступать с этих точек, и команда считывания информации.

Г1ри отработке кадра, содержащего признак начала проверки, узел 3 синхронизации выдает команду распределителю на запись

«1» во все логические ячейки !2 по входу

23, а узлу считывания 1 — команду на ввод сггедугощего кадра. При считывании кадр2 во входной регистр 7 записывается адрес входной точки проверяемого блока, 2 формирователь 19 пришгмает команду записи. 1 ак как в исходном состоянии в логических ячейках 12 установлены «1», то IIO r.ðorp2ìxiå B логические ячейки 12 запись(вается только сигнал «О». Во время отработки введенного кадра rio сигналу узла 3 синхронизации формирователь 19 производит подключение Входного регистра 7 к дешифратору 10 и распределитель 20 по входу 22 запись «О» в выбранную логическую ячеЙку; с выхода которой сигнал «0» через выходную точку, например

13 — 2, подастся на вход проверяемого о;10ка. После отработки кадра вводится и отрабатывается следующий кадр и т. д.

В момент когда будут отработаны Все кадры с входными адресами и признаками входных величин, с выхода элемента ИЛИ 11 на вход проверяемого блока поступит код, заданный в программе., Проверка выходных сигналов блока производится при отработке кадров, содержащих адреса выходных точек. Г1ри считывании таких кадров входной регистр 7 принимает. адрес выходной точки проверяемого блока, формирователь 19 — сигнал «О» или

«1», который должен быть на этом выходе, а элемент И 16 — команду считывания. При отработке кадра формирователь 19 производит подключение входного регистра 7 к дешифратору 10, а распределитель 20 по входу 21 осуществляет считывание информации из выбранной ячейки 12. Сигнал « l » на выходе логической ячейки 12 появится в случае прихода «1» с контролируемого блока через вход, например, 13 — 1. Если с контролируемого блока приходит сигнал «О», то элемент И 16 закрывается этим потенциалом.

Выход триггера 15 ячейки отключается диодом 14 от входа элемента И 16, потому что на анод диода подается сигнал «О». а на катод — «!», С выхода выбранной логической ячейки

12 считывается сигнал «О». Сигналы с выхода элемента ИЛИ 11 запоминаются сдвиговым регистром 17. Формирователь 19 по сигналам дешифратора !8 и командам узла

З0

55 считывания 1 дает заключение о правильности работы блока. Если сигнал на выходе проверяемого блока соответствует заданному в программе, то вводится и отрабатывается следующий кадр, а если не соответствует — осуществляется останов.

Таким образом, достоверность контроля монтажа повышается за счет двойного и инверсного опроса адресов, а также за счет выявления при проверке сбоев, вызванных неисправностью устройства или случайным

ВНЕШНИМ ВОЗДЕйетВИЕМ., CTi 0!ICiВ(. Д1Я KOHT POЛЯ:=Э;! ЕКТРПЧЕСКОГО .!Онтажа,:0. je,)æаirjc(дс! !и с!)РггтОР,,10ги I2cKl!(ячег(ки па. гя:li, 3(:л счп i ы Вапия, мзс 1 и ндикаци:г, мзег! Синхгэонизацпи, х зсл анализа, два Вхо.шь(х регистра и элем HT И, 1И)

iHpliHBxI каждый выход дешифратора i!OJ,—

l1(ii)B0. ыо.jx cooTBCTcTBX 10!)jan É логической ячейки памяти, первый Bblxo1, которой соединен с соответств)югцим в ходом устройств;., первый Вход узла анализа соединен с Bhixorlox! э. iBмеггта Р171И, Bxo;jbl которого сое1ин(пы со вторыми выходами соответстг)угогцггх логических ячеек памяти, входы опроса которы соединены соответственно с выходами опроса узла анализа, ВЫХОД (З,га C !IIThiBBi!i!H ПОДК1(ОЧЕН KO Б\ОДа. Iiсг)ВОСО г! BTOPÎÃO ВХОДНЫХ ОЕ! ИСТ Ров, ьторому Входу узла анализа и первым входа. i уз. га сичх! Онпзации и мзла гlндикации, второй Вы.,сд узла анализа подключен KG

Вторых! Вход2м "зла пндггкс1ции II узла сННхрониза цпп., !!I(".pBI il Выход которого соедиliBí со входом узла считывания, третий вход и второй выход узла синхронизации соединены соответственно сo Вторым выходом и третьим входом узла анализа, от.гггчающееег и xi, что, с целью повышения достоверности

K0iiTDO.! R. B X СТРО,CT I30 ВВЕДЕН Ь! МЗЕЛ П PCключепия, регистр текущегo адреса и схема сравнения 2,1påñîBi причем, третий и четзертый Выходы узла анализа подключены

СООТВЕ1 СТВЕННО КО BX03X Pt ГИСТР2 ТЕКХ ШЕго адреса и первому входу узла переключения, вь)ход которого соединен со входом дешифратора. Входы схемы сравнения адресов подклпочены к выходу второго входного ре-! ИСТР2 li (IB;1!3OX!T ВЫХ01(РЕГHCTP3 ТЕКМ)ЦЕI() адреса, .лорой вход которого и выход перВог0 в: од;юго регистра подключены соответственно ко второмх и третьему входам узла псреклю-!0!l! IH, выход схемы сравнения адресов соедин!СИ с четвертым входом узла ан<3,1иза.

Источники Информации, принятые во Внимание I!p!i экспертизе:

l. Авторское с в пдетел ьств о LCC. Ð .х(3 45529!), кл. С) !)1 1х 31,02, 1973.

2. Лг)ropcKnc свидстсзгьст((о СССР ,х,е 482. 26, кл. (з 05 Б 23, !)0 !97- . .

634291

Составитель В. Вертлиб

Редактор Д. Мепуришвили Техред О. Луговая Корректор С. Шекчар

Заказ 6763/47 Тираж 784 Подписное

LLHHHHH Государственного комитета Совета Министров СССР по делам изобретений ч открытий ! 3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент>;, г. Ужгород, ул. Проектная.