Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ.

Союз Советскии

Социалистимескитт

Республик л 634374

К АВТОРСКОМУ СВИДИТЕЛЬСТВУ / (6!) Дополнительное к авт. свил-ву— (22) Заявлено 29.12.75 (21) 2310578/18-24 с присоединением заявки Хе 2368230/18-24 (23) Приоритет г (51) М, Кл. (11 С 27/00

Госудврственнь!й комитет

Саветв Министров СССР по делам иэобретений н открытий (43) Опубликовано25.11.78.Бюллетень о43 (53) УЛК 681.327. .66(088.8) (45) Лата опубликования оттисакия 26 11.78 (72) Авторы изобретения

Г. Н. оахгиаров и П. А. Пзарданов (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может найти применение при построении аналого-цифровых преобразователей, устройств дискретной и цифровой фильтрации и других устройств, использующих гибридные и цифровые мегоды.

Известно аналоговое запоминающее устройство, которое содержит мостовой диодный ключ, управляемый генераторами тока (lf

Недостатком такового устройства является сложность формирования идентичныхх разнополярных отробов, что ограничивает его динамический и часгогный диапазоны.

Известно также устройство, содержащее последовательный ключ на полевом транзисторе (2j .

Его недостатком является наличие зна- 2О чительных помех через межэлектродные емкости на выход устройства, что ограничивает точность его работы и бысгродей» сгвие.

Наиболее близким техническим решением является аналоговое запоминающее устройство, содержащее шесть транзисторов, первые четыре иэ которых соединены по мостовой схеме, причем базы первого и второго транзисторов объединены, эмитгеры третьего и четвертого гранзиогоров соединены с одной иэ обкладок конденсатора и выходом устройства, другая обкладка конденсатора соединена с шиной нулевого потенциала, эмиггеры пятого и шестого транзисторов подключены к базам третьего и четвертого транзисторов соответственно, резистор, шину сгробнрующей го импульса и генераторы тока (3) .

Недостатками его являются зависимость амплитуды действующих в схеме стробов ог верхней границы динамического диапазона входного сигнала, что при заданной максимальной мощности рассеяния всего устройства ограничивает как его динамический диапазон, гак и быст родейсгвие, наличие апертурной неопред пенности порядка нескольких наносекунд, определяемой временем раэмыкания клю634374 чеВых транзисторов, ограниченная точ. ность в режиме хранения, однополярность схемы и невысокое входное сопротивление, определяемое используемыми на входе резисторами. 5

Бель изобретения - увеличение точности и быстродействия устройства.

Поставленная цель достигается тем, что оно дополнительно содержит восемь. транзисторов, базы седьмого, восьмого, ® девятого и десятого транзисторов подключены к одной из обкладок конденсатора, базы пятого и шестого транзисторов соответственно соединены с эмиттерами седь мого и восьмого, девятого и десятого с базами одиннадцатого и двенадцатого транзисторов и с выходами генераторов тока, эмиттеры одиннадцатого и двенадцатого транзисторов подключены соответственно к коллекторам девятого и восьмого транзисторов, входы генераторов тока соединены с шиной стробирующего импульса, коллектор тринадцатого транзистора и кол лектор четырнадцатого транзистора соеди иены соответственно с отрицательной и положи тельной шинами пи тания, эми ттеры тринадцатого и четырнадцатого транзиоторов соединены с базами первого и второго транзисторов и через резистор - со входом устройства, база тринадцатого транМ зистора соединена с эмиттером восьмого транзистора, а база четырнадцатого транзистора соединена с эмиттером девятого транзистора.

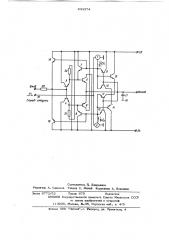

Сущность изобретения поясняется чертежом, на котором изображена электриче ская схема устройства.

Устройство содержит генераторы тока

1 и 2, транзисторы 3,4,5 и 6, образующие эмиттерный повторитель, транзисторы ©

7 - 16, причем транзисторы 7,9,10,13 и 15 образуют одно иэ плеч управления, а транзисторы 8,11,12,14 и 16 - другое плечо управления, конденсатор 17, при этом пары транзисторов разного типа про- 5 водимости 9-10 и 11-12 представляют собой двухсторонние ограничители напряжения относительно напряжения на конденсаторе 17, а транзисторы 7 и 8 предназначены для коммутации режимов работы yet ройства, которое также содержит шину нулевого потенциала 18, шину стробирующего импульса 19, резисторы 20,21 и 22, положительную 23 и отрицательную 24 шины питания.

Устройство работает следующим образом и имеет два режима работы. В первом из них оно представляет собой буферное устройство, имеющее высокое входное и малое выходное сопротивление . При этом напряжение, действующее на его входе,отслеживается на конденсаторе 17, являющемся его выходом. Во втором режиме устройство выполняет функцию разомкнутого ключа, при этом на конденсаторе 17 сохраняется то напряжение, которое было на нем в момент переключения из первого режима во второй.

Указанные режимы работы устройства определяю тся по тенци алом, поступающим на шину стробчрующего импульса 19. При наличии на этой шине разрешающего потенциала генератор тока 1 выдает втекающий в эмиттер транзистора 9 ток +У, а генер а тор тока 2 - вы текающи и из э ми т тер а транзистора 12 ток -У, поэтому транзисторы 9 и 12 открыты. При этом транзисторы 3,4 и 5,6 будут открыты, а транзисторы 7,8, 10, 1 1, 1 3 —. 16 полностью закрыты. Эмиттерный повторитель на транзисторах 3,4,5 и 6 в этом режиме замкнут на конденсатор 17 и поэтому напряжение на нем отслеживает входное напряжение

При подаче на шину стробирующего ймпульса 19 запрещающего потенциала происходит синхронное изменение полярности токов генераторов 1 и 2 без изменения .их величины. При этом транзисторы 9 и, 12 запираются, а.транзисторы 10 и 11 открываются. Потенциал в точке связи эмиттеров транзисторов 9 и 10 падает приблизительно на 1,4 вольта, а в точке связи эмиттеров транзисторов 11 и 12 он возрастает в то же время приблизи— тельно на 1,4 вольта. Величина этих перепадов, действующих синхронно, вполне достаточна для очень быстрого запирания всех четырех транзисторов эмиттерного повторителя (на транзисторах 3,4,5 и 6), что и приводит к невозможности дальнейшего изменения заряда на конденсаторе

17.

В то же время напряжения в коллекторных цепях транзисторов 10 и 11 ока, зывается привязанным к напряжению на конденсаторе 17, через открытые транзиctopbl 14 и 13, которые используются как "плавающие" источники питания, повторяющие напряжение на конденсаторе 17.

Последнее обстоятельство стабилизирует величину базовых токов 10 и 11, являющихся токами утечки конденсатора

17, и, следовательно, появляется возможность компенсации этого тока утечки.

634374

Кроме того, в этом режиме оказывается замкнутым контур, состоящий из транзисторов 10, 11, 15 и 16.

Тем самым напряжение с конденсатора 17 подается на резистор 22. Образующийся при этом делитель напряжения, состоящий из резистора 22 и входного сопротивления контура, позволяет в коэффициент леления делителя раз уменьшить погрешность, определяемую проле- 1© танием входного мгновенного значения сигнала.

Поскольку размыкание эмиттерного повтори теля осущес твляе тся путем замыкания эмиттерных токов транзисторов 3 и 4, в М также базовых токов транзисторов 5 и 6 в эмиттерные цепи отпирающихся транзисторов 7 и 8 соответственно, управляемых в свсяо очередь небольшими и быстрыми перепадами напряжения, прикладываемыми ® к их базам, ro время раэмыкания, опреде.ляемое в основном временем, необходимым . для рассасывания накопленных неосновных носителей в базах транзисторов 5 и 6, оказывается весьма незначительным. Это обеспечивает апертурную неопределенность порядка 1 нс. Полная симметрия схемы устройства относительно нулевого уровня обеспечивает работу or биполярных входных сигналов.

Предложенное устройство обеспечивает технические характеристики при небольших мощностях рассеивания, что делает возможным его производствометодами гибрндной и интегральной технологии и обуславливает высокую технико-экономическую эффективность применения.

Формула изобретения

Аналоговое запоминающее устройство, содержащее шесть транзисторов, первые четыре из которых соединены по мостовой схеме, причем базы первого и второго транзисторов объединены, эмиттеры третьего и четвертого транзисторов соединены с одной из обклалок конденсатора и выходом устройства, другая обкладка конденсатора соединена с шиной нулевого потенциала, эмиттеры пятого и шестого транзисторов подключены к базам третьего и четвертого транзисторов соответственно, резистор, шину стробирующего импульса и генераторы тока, о т л и ч а ю щ е е с я тем что с целью увеличения точности и быстродейст. вия, оно дополнительно содержит восемь транзисторов, базы, сеаьмого, восьмого, девятого и лесятого транзисторов подключены к одной из обкладок конденсатора, бвэы пятого и шестого транзисторов соответственно соединены с эмиттером седьмого и восьмого, девятого и десятого, с базами одиннадцатого и двенадцатого транзисторов и с выходами генераторов тока, эмиттеры одиннадцатого н двенадцатого транзисторов подключены соответственно к коллекторам девятого и восьмого гранэисторов, входы генераторов тока соединены с шиной стробирующего импульса, коллектор тринадцатого транзистора и коллектор четырнадцатого транзистора;соединены соответственно с отрицательной и положительной шинами питания, эмиттер тринадцатого и четырнадцатого транзисторов соединены с базами первого и второго транзисторов и через резистор — co входом устройства, база тринадцатого транзистора соедннена с эмиттером восьмого транзистора, а база четырнадцатого транзистора соединена с эмиттером девягого транзистора.

Источники информации, принятые во внимание при экспертизе:

).ТЕЕЕ Trans.onе гсо и T8eor, 1964, I/. СТ-11, Л 3, р. 389-396.

2. Приборы и техника эксперимента, 1972, No 3, crp. 107-109.

3. Авторское свидетельство СССР

Мо 484637, кл. Н ОЗ К 13/02, 17.02.73

634374 вход утро

Сосгавитель П. йзардаиов

Редактор А, Садомов Текред С. Мигай Корректор А. Власенко

Заказ 6772/52 Тираж 675 Подписное

ЦНИИПИ Государственного комигега Совега Министров СССР по делам изобретений и огкрыгий

113035, Москва, Ж-35, Раушскаа наб., д. 4/S

Филиал ППГ! Патент, r. Ужгород, ул. Проекгнаи, 4