Устройство для асинхронной передачи цифровой информации по синхронному каналу связи

Иллюстрации

Показать всеРеферат

-- -х; . ;

О П И С А Н И Е 11;g3gggg

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 02.02.77 (21) 24487 26/18-09 с присоединением заявки №

2 (51) М. Кл.

H 04 J 3/06

Государстееиный иомнтет

Совета Мннистроа СССР оо делам изооретеннй и открытий (23) Приоритет (43) Опубликовано 25.11.78.Бюллетень ¹43 (53) УДК621.396.4 (088.8) (45) Дата опубликования описанияэ8.11.78 (72) Авторы изобретения

В. С. Мальков, Ю. М. Елисеев и В. B. Згурекий (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОЙ ПЕРЕДАЧИ

ЦИФРОВОЙ ИНФОРМАЦИИ ПО СИНХРОННОМУ КАНАЛУ

СВЯЗИ

1 2

Изобретение относится к многоканальной цифровой аппаратуре связи, в частности к устройствам для асинхронной передачи цифровой информации от автономных источников по синхронным каналам связи многоканальных импульсных систем с временным уплотнением каналов.

Известно устройство для асинхронной передачи цифровой информации по синхронному каналу связи, содержащее фазовый дискриминатор, выходы которого соединены с первым и вторым входами управляемого делителя, третий вход которого соединен с задаюшим генератором, а выход — с первым входом блока регистрации, второй вход которого соединен с сигнальным входом фазового дискриминатора (1).

Однако такое устройство обладает недостаточной устойчивостью синфазной работы.

Целью изобретения является повышение устойчивости фазирования.

Для этого в устройство для асинхронной передачи цифровой информации по синхронному каналу связи, содержащее фазовый дискриминатор, выходы которого соединены с первым и вторым входами управляемого делителя. третий:|од которого соединен с задаюгцпм генератором, а Выход — с первьк

Это устройство имеет повышенную устойчивость фазирования.

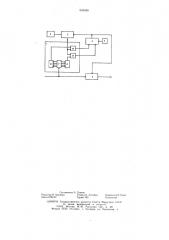

На чертеже изображена структурная электрическая схема п едложенного устройства.

634466 равляемого делителя 2 подаются на вход анализатора 5 двойного стробирования, который ьырабатывает сигнал в том случае, кoräÿ на один такт частоты этих импульсов

Оно содержит фазовый дискриминатор 1, выходь. которого соединены с первым и вторым входами управляемого дел. геля 2, третий вход когорого соединен с задаюц;им генератором 3, а выход — с первым входом блока 4 регистрации, второй вход которого соединен с сигнальным входом фазового дискриминатора 1, введенный анализатор 5 двойного стробирования, вход которого соединен с выходом управляемого делителя 2, а выход — с входом фазового дискримина- 10 тора 1, причем на другой вход анализатора 5 двойного cTpoc ирования подан сигнал от источника 6 импульсов стробирования. Фазовый дискриминатор содержит регистр сдвига 7, выходы которого через соответствующие первый и второй анализаторы 8 и 9 комбинаций двоичного кода соединены с первыми входами двух блоков совпадения

10 и 11, вторые входы которых являются входом фазового дискриминатора 1, сигнальным входом которого является вход регистра сдвига 7, а выходы блоков совпадения .10 и 11 являются выходами фазового дискриминатора 1.

Устройство работает следующим образом.

Принятый сигнал поступает на входы фазового дискриминатора 1 и блока 4 регистрации. Длительность и частота импульсов импульсной последовательности входного сигнала равны длительности и частоте импульсов источника 6 импульсов стробирования, подаваемых на вход анализатора 5 двойного стробирования. Наличие импульса в принятом сигнале за один такт частоты его ввода соответствует приему посылки определенной полярности, отсутствие импульса соответствует приему посылки противоположной полярности. Посылки в синхронном канале связи являются результатом строоирования посылок входного сигнала импульсами стробирования на передающем конце канала связи. Стробирование производит40 ся импульсами, частота следования которых равна частоте ввода сигнала в синхронный канал связи — 1.. Процесс стробирования входного сигнала осуществляется с помощью блоков совпадения 10 и 11, на первые входы которых подаются посылки входного сигна- 45 ла, а на другие входы узкие, то есть имеющие большую скважность импульсы стробирования. Результат стробирования представляет собой последовательность узких импульсов, следующих с частотой

На приемном конце канала связи принятый сигнал можно рассматривать как посылки входного сигнала совместно со вспомогательными посылками, дублирующими некоторые посылки входного сигнала. Импульсы с упна другой его вход поступают два импульса стробирования, следующих с частотой f„. В момент выхода сигнала с анализатора 5 двойного стробирования первый и второй анализаторы 8 и 9 могут либо вырабатывать импульсы, либо не вырабатывать их, в зависимости от структуры принятого сигнала и от величины рассогласования фазы частоты, вырабатываемой управляемым делителем 2 частоты, относительно принятого сигнала. Сигналы с выходов фазового дискриминатора 1 управляют работой делителя

2. Принятый сигнал восстанавливается в блоке 4 регистрации с помощью импульсов, поступающих с управляемого дели råëÿ 2, и подается к приемнику цифровой и .формации.

Применение предложенного устройства для асинхронной передачи цифровой информации по синхронному каналу связи позволяет повысить устойчивость фазирования частоты выходного сигнала известных коррекционных устройств при сокрашении минимальной задержки информации в тракте передачи и приема.

Формула изобретения

1. Устройство для асинхронной передачи цифровой информации по синхронному каналу связи, содержащее фазовый дискриминатор, выходы которого соединены с первым и вторым входами управляемого делителя, третий вход которого соединен с задающим генератором, а выход — с первым входом блока регистрации, второй вход которого соединен с сигнальным входом фазового дискриминатора, отличающееся тем, что с целью повышения устойчивости фазирования, введен анализатор двойного стробирования, вход которого соединен с выходом управляемого делителя, а выход — с входом фазового дискриминатора, причем на другой вход анализатора двойного стробирования подан сигнал от источника импульсов стробирования.

2. Устройство по п. 1, отличающееся тем, что фазовый дискриминатор содержит регистр сдвига, выходы которого через соответствующие первый и второй анализаторы комбинаций двоичного кода соединены с первыми входами двух блоков совпадения, вторые входы которых являются входом фазового дискриминатора, сигнальным входом которого является вход регистра сдвига, а выходы блоков совпадения являются выходами фазового дискриминатора.

Источники информации, принятые во внимание при экспертизе:

1. Шляпоберский В. И. Основы техники передачи дискретных сообщений. М., «Связь», 1973, с. 257 — -259.

634466

Составитель А. Грачев

Редактор Н. Хлудова Техред О. Луговая

Заказ 6781/57 Тираж 763

Корректор Е. Папп

Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открьний

I 13035, Москва, Ж-35. Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4