Стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН И Я ц63547О

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 05.01.76 (21) 2310845/24-07 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.11.78. Бюллетень № 44 (45) Дата опубликования описания 30.11.78 (51) Я, Кл з

G 05F 1/56

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621 316.722. .1(088.8) (72) Авторы изобретения

8. И. Штильман и А. Ю. Шостак (71) Заявитель (54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

2 /кэ мин /э в + /кБ

Изобретение относится к области электротехники и может быть использовано в источниках электропитания электротехнической и радиотехнической аппаратуры.

Известен транзисторный стабилизатор постоянного напряжения компенсационного типа, содержащий регулирующий элемент, усилитель постоянного тока, источник опорного напряжения. Недостатком известного устройства является ограниченный КПД из-за того, что падение напряжения на регулирующем транзисторе не может составить величину менее 0,8 — 1,5 В.

Из известных стабилизаторов постоянного напряжения наиболее близким к предлагаемому по технической сущности является стабилизатор постоянного напряжения, содержащий включенный последовательно в выходную шину регулирующий транзистор, дифференциальный усилитель постоянного тока, один вход которого соединен с выходом резисторного делителя, включенного между выходными гыводами.

В известном стабилизаторе переход эмиттер — база регулирующего транзистора смещен в прямом направлении, а переход коллектор — база — в обратном. Поэтому минимальное падение напряжения па регулирующем транзисторе определяется по формуле и составляет величину 0,8 — 1,5 B. При увеличении нагрузочного тока данного стабилизатора требуется применение составного регулирующего транзистора. При этом минимальное падение напряжения Укэ„„„ превышает 1,5 В и КПД также уменьшается.

I0 Целью изобретения является повышение

КПД путем снижения падения напряжения на рсгулирующем транзисторе.

Указанная цель достигается тем, что стабилизатор постоянного напряжения

15 снабжен двумя усилительными каскадами на транзисторах, причем база транзистора первого усилительного каскада соединена с выходом дифференциального усилителя постоянного тока, эмиттер — с отрицательным

20 выходным выводом, а коллектор через резистор — с положительным выходным выводом, а второй усилительный каскад выполнен по схеме составного транзистора на транзисторах разного типа проводимости и

25 подключен входом и коллектору транзистора перво-о усилительного каскада, а выходом — к базе регулирующего транзистора.

В результате такого соединения переходы коллектор — база и эмиттер — база регулиру30 ющего транзистора смещены в прямом на635470 правлении и минимальное напряжение на переходе коллектор — эмиттер регулирующего транзистора определяется по формуле

Укэ„„„= Уэв — Uzs = О (2) причем ток базы регулирующего транзистора является током эмиттера (коллектора) транзистора второго усилительного каскада.

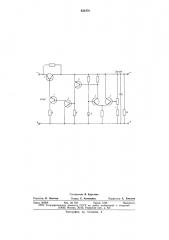

На чертеже представлена принципиаль- 10 ная электрическая схема стабилизатора постоянного напряжения.

Транзисторный стабилизатор постоянного напряжения содержит последовательно включенный в выходную шину регулирую- 15 щий транзистор 1 и дифференциальный усилитель постоянного тока на транзисторах 2, 3, причем вход транзистора 3 соединен с выходом резисторного делителя 4, включенного между выходными выводами; 20 первый усилительный каскад на транзисторе 5, база которого соединена с выходом дифференциального усилителя постоянного тока, эмиттер — с отрицательным выходным выводом, а коллектор через резистор 25

6 — с положительным выходным выводом; второй усилительный каскад, выполненный по схеме составного транзистора на транзисторах 7 разного типа проводимости с резистором 8 в коллекторной цепи, причем 30 вход второго усилительного каскада подключен к коллектору транзистора 5 первого усилительного каскада, а выход — к базе регулирующего транзистора 1; источник опорного напряжения на стабилитроне 35

9, нагрузочный резистор 10.

Стабилизатор работает следующим образом.

Допустим, что входное напряжение стабилизатора постоянного напряжения сни- 40 жается. При этом в первый момент времени напряжение на нагрузочном резисторе

10 также снижается, снижается проводимость транзистора З,-,дифференциального усилителя постоянного тока, а проводимость 45 транзистора 2 увеличивается, что сопровождается увеличением проводимости усилительных каскадов, выполненных на транзисторах 5 и 7, и регулирующего транзистора 1. При этом напряжение на выходе 50 схемы возвращается к исходной величине.

Транзисторы 1, 2, 3, 5, 7 работают в линейном режиме.

Соблюдается условие (3) 55 где Is, 1к, P — соответственно токи базы и коллектора, и коэффициент усиления соответствующих транзисторов 1, 2, 3, 5, 7.

При дальнейшем уменьшении входного напряжения ток базы регулирующего транзистора 1 возрастает и вместо условия (3) для регулирующего транзистора 1 выполняется условие (lyI (4) ь где 1 в, k,, р — соответственно токи базы и коллектора, коэффициент усиления регулирующего транзистора 1.

При этом второй усилительный каскад переходит из линейного режима в режим насыщения и ток базы Is, регулирующего транзистора 1 ограничивается только резистором 8. Переход коллектор — база регулирующего транзистора 1 смещается в прямом направлении и падение напряжения на этом переходе компенсирует падение напряжения на переходе эмиттер †ба регулирующего транзистора 1, Напряжение Укэ„„„ регулирующего транзистора 1, ранее определявшееся по формуле (1), теперь определяется по формуле (2).

Поскольку падение напряжения на переходе коллектор — эмиттер регулирующего транзистора 1 резко уменьшается, КПД стабилизатора постоянного напряжения повышается.

Формула изобретения

Стабилизатор постоянного напряжения, содержащий включенный последовательно в выходную шину регулирующий транзистор, дифференциальный усилитель постоянного тока, один вход которого соединен с выходом резисторного делителя, включенного между выходными выводами, отлич а ю шийся тем, что, с целью повышения

КПД путем снижения падения напряжения на регулирующем транзисторе стабилизатора, он снабжен двумя усилительными каскадами на транзисторах, причем база транзистора первого усилительного каскада соединена с выходом дифференциального усилителя постоянного тока, эмиттер — с отрицательным выходным выводом, коллектор через резистор — с положительным выходным выводом, а второй усилительный каскад выполнен по схеме составного транзистора на транзисторах разного типа проводимости и подключен входом к коллектору транзистора первого усилительного каскада, а выходом — к базе регулирующего транзистора.

635470

Составитель В. Круглова

Техред С. Антипенко

Редактор В. Девятов

Корректор E. Хмелева

Типография, пр. Сапунова, 2

Заказ 2059/4 Изд. Ыв 742 Тираж 1005 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5