Цифровой фильтр

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Севаз Сееетскнк

Соцнапистнчески я

Республик (61) Дополнительное к авт. свил-ву (51) М. Кл.

506 Г 15/34 (22) 3аявлено 180375 (2l) 2114491/18-24 с присоединением заявки РЙ (23) Приоритет— (43) Опубликовано 051278.6þëëåòåíü ЭЙ45 (45) Дата опубликования описания 05.12.78

Государственный комитет

Совета Министров СССР

00 делам изобретений и открытий (И) УДК 631. 326 (088.8}

{72) Авторы (54} ЦИфжвой фильтр

Предлагаемое изобретение относится к специализированным средствам вычислительной техники и может быть использовано для обработки информации. б

Известно устройство (1), содержащее блоки памяти, сумматор, умножитель, промежуточные регистры, которое позволяет осуществлять фильтрацию сигналов на основе цифровых мето- дов.

Наиболее близким по технической сущности и достигаемому результату является устройство (2), содержащее блок памяти весовых коэффициентов, первый вход которого является входом записи коэффициентов фильтра, второй вход и выход соединены соответственно с первым адресным счетчиком и входом первого регистра, выход которого соединен с первым входом умножителя, соединенного своим выходом со входом накопительного сумматора, выход которого соединен с цифроаналоговым преобразователем, два блока памяти входных отсчетов, первые входы которых соединены со вторым и третьим адресными счетчиками соответственно, при этом второй вход н выход первого блока памяти входных отсчетов соедииены соответственно с выходом второго и первым входом третьего регистров, выход третьего регистра соединен со входом второго регистра, а второй вход третьего регистра является входом отсчетов входного сигнала фильтра.

Указанные устройства для цифровой фильтрации имеют низкое быстродействие для случая симметричных весовых коэффициентов фильтра.

Целью изобретения является увеличение быстродействия фильтра для указанного частного вида весовых коэффициентов.

Укаэанная цель достигается тем, что в устройство введены четвертый н пятый регистры и сумматор, первый н второй входы которого соединены с выходами соответственно третьего и четвертого регистров, выход — co вторым входом умножнтеля, при этом первый н второй вход пятого регистра соединены со входами соответственно второго и четвертого регистров, а второй вход н выход второго блока памяти входных отсчетов соединены соответственно с выходом пятого и входом четвертого регистров.

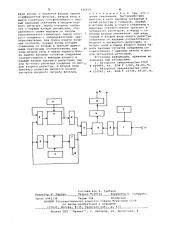

На чертеже представлена блок-схема цифрового фильтра, где 1 — блок памяти

636616 весовых коэффициентов; 2,3,4 — первый, второй и третий адресные счетчики1 5 — 9 — регистры с первого по пятый соответственно;10, 11 — первый и ,второй блоки памяти входных отсчетов;

1 2 — сумматору 1 3 — умножи телЫ 14 накопительный сумматор1 15 — цифроаналоговый преобразователь; 16 — вход отсчетов входного сигнала фильтра;

17 — вход записи коэффициентов фильтра.

Устройство фильтрует сигнал путем вычисления свертки входных отсчетов

Х „ и весовых коэффициентов Фильтра т) по формуле и

М-f K h (Х + Х + Ь - Х э,р я ээ- н м-2м+1э} э м-утф

Работа цифрового фильтра сводится к следующему. Коэффициенты 4„ при

О и М, соответствующие полпериоду весовой функции, хранятся в блоке 1 З) памяти весовых коэффициентов. Текущий отсчет входного сигнала Х 1э записан в регистр 7, отсчеты Х,э „ при 1 и М хранятся в блоке 10 памяти входных отсчетов, а для М +((и «с 2М в блоке 11 памяти входных отсчетов. Вычисление согласно (1) начинается считыванием коэффициентов Ао из блока 1 в регистр 5 при соответствующем состоянии адресного счетчика 2. Одновременно значение Х„э>< перезаписывается из блока 11 памяти входных отсчетов 11 в регистр 9 в режиме считывание при адресе, установленном в адресном счетчике 4. Затем производится суммирование входных отсчетов Х <+ Х э „„35 сумматором 12 с последующим вычислением произведения " (Õ Х э „„) на матричном устройстве 13 умножения. По истечении времени, необходимого на умножение, произведение добавляется в 40 накопительный сумматор 14. Отсчет входного сигнала одновременно с поступлением в сумматор 12 перезаписывается в регистр 6. Затем в устройство происходит перезапись Ь, иэ 1 в регистр

5 и отсчетов Х э иэ блока 10 памяти входных отсчетов в регистр 7, а Х э g q< из блока памяти ll входных отсчетов одн эвременно в регистры 9 и 8. Вслед за c"читыванием Х, по его адресу, уста эовленному в адресном счетчике 3, записывается отсчет Х из регистра 6.

Одновременно отсчет Х,<перезап сывается иэ регистра 9 в блок 11 памяти входных отсчетов вместо уже сосчи55

TBHIIoI в предыдущем цикле отсчета

Х для этого устанавливается соотV- гм ветствующий адрес в адресном счетчике 4. После этих перезапж.ей устройством выполняется сложение с IIîcëå -1 h э -гм-+4

1э + . ) 60 затем произведение добаьлн«тся II I аКОпительный сумматор 14. В фильтре происходит повторение таких вычислительных циклов М ра-э, в результате которых последовательно QGpазу н)TcR прои.-эя»- ;5

ДениЯ Èä (Х эп+ Xv-2M II) ДлЯ О< n M-э.

В последнем (М + 1) -м цикле в умножителе 13 вычисляется произведение П Х „ . Отсчет Х э м хРанитсЯ при этом в регистре 7, в который он перезаписан из второГо бл .ка памяти входных отсчетов 11, затем этот отсчет перезаписывается в регистр 8.

ВСЛЕД За ЭТИМ Хэ-M ПЕрЕЗаПИСЫвается из регистра 8 в блок 11 памяти входных отсчетов в адрес уже сосчитанного отсчета Х )м . Одновременно с добавлением в накопительный сумматор 14 М+1 -го произведения в регистр 7 записывается следующий входной отсчет Х ), - После чего вычисленное значение У э может нылаваться в дискретной форме из накопительного сумматора 14 и в непрерывной — с цифроанаЛогового преобразователя 15, после чего сумматор 14 обнуляется.

К этому моменту произошел сдвиг входных отсчетов на период дискретизации при неизменном положении весовых коэффициентов. Дискреты входного сигнала получили следующее распредеение Х y«s регистр отсчеты Х >, м для 14 и М в блоке

10 и при М + 1 гэ 2М в блоке 11.

Последний входной отсчет Х 2м при вычислении У э -ro значения после обработки отбрасывается. В результате этого Фильтрация следующего отсчета У1э+.э будет производиться с временным окном, сдвинутым на период квантования.

Перестройка фильтра на новую амплитудно-частотную характеристику осуществляется в течение одного такта вычисления свертки путем записи каждого нового и -го коэффициента в блок 1 памяти весовых коэффициентов фильтра в течение вычисления соответствующей и-й арифметической операции под знаком суммы в формуле (1), выполняемой комбинационным сумматором и матричным множительным устройством.

Новая организация памяти отсчетов входного сигнала с помощью дополнительных двух регистров и подключение к выходным регистрам блоков памяти входных отсчетов сумма.,эра, выход которого подается на один из входов матричного устройства умножения, позволяют сократить время вычисления одной выходной дискреты (или такт вычисления свертки) до длительности М+1 операцией умножения, т.е. повысить быстродействие 11Ф в два раза по сравнению с быстродействием известного цифрового нерекурсивного Фильтра.

Формула изобретения

Цифровой фильтр, содержащий блок памяти весовых коэффициентов, пе1вый

6366) 6 — с л

Составитель И. Грибнон

Редактор Б. Герцен Техоед N.Ïåòêî Корректор A. Грицен»<о

Заказ 6942/39 Тираж 784 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035 Москва, Ж-35 Раушская наб.с д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 вход которс о является входом записи коэффициентов фильтра, нторой вход и выход соединены соответственно с первым адресным счетчиком и входом первого регистра, ныход которого соединен с перным входом умножителя, соединенного своим выходом со входом накопительного сумматора, выход которо»о соединен с цифроаналоговым преобразователем, дна блока памяти нходных отсчетов, первые входы которых соединены со вторым и третьим адресными счетчиками соответственно при этом второй вход и выход первого блока памяти входных отсчетов соединены соответственно с выходом второго и первым входом третьего регистров, выход тр"тьего регистра соединен со вхо-i дом второго регистра, а второй вход третьего регистра является входом отсчетов входного сигнала фильтра, о т л»» ч а ю щ и и с я тем, что с целью у величения быстродействия фильтра в него введены четвертый и пятый регистры и сумматор, первый и второй входы и» торого соединены с выходами соответственно третьего и четвертого регистров, а выход — со вторым входом умножителя, при этом первый и второй вход пятого регистра соединены со входами соответственно второго и четвертого регистров, а второ». вход и выход второго блока па0 мяти входных отсчетов соединены соответственно с выходом пятого и входом четвертого регистров.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

9 466499, кл. 5 06 < 1/02, 06.03.74.

2. Авторское свидетельство СССР

9 516043, кл. 6 06 F 15/36, 03,07.74.