Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

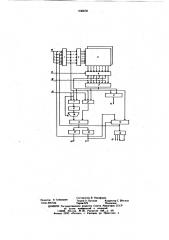

636678 с возможностью чтения заранее заданных значений прямых и инверсных кодов адресов ячеек. Усилители считывания -- записи 4 имеют возможность переключения вхолов управляющим сигналом, определяющим режим работы запоминающего устройства. Регистр слова 5 служит для фиксации в рабочем режиме и режиме восстановления слов информации, считанных иэ блока запоминающих матриц 3, либо предназначенных для записи в блок 3, а в контрольном режиме — значений прямого и инверсного кодов адреса ячейки, в которую произошло обращение при считывании из блока 3.

Блок контроля информации 6 функционирует в рабочем режиме и служит для проверкй содержимого регистра слова 5 и регист!

5 ра адреса I перел записью информации в блок 3 и для проверки информации, прочитанной из блока 3 на регистр 5 и выработки сигнала неисправности ОЗУ в случае искажения прочитанной информации.

Блок вычитания инверсных кодов адре- 20 са 7 предназначен для вычитания в контрольном режиме из инверсного кода адреса (а), считанного иэ постоянной запоминающей части блока 3 на регистр 5, инверсного кола адреса (в), хранящегося на регистре 1. причем, прямое и инверсное значений разности определяются, соответственно формула ми с; =а,Ь; и ci =а;ЬчЬ, Блок вычитания прямых кодов адреса 8 служит для вычитания по модулю два в контрольном режиме из прямого ода адреса, считанного из ПЗЧ блока 3 на регистр 5, прямого кода адреса, хранящегося на регистре 1. Элементы И 10 предназначены для клапанирования на вход сумматора 11 только тех инвертированных разрядов разности с выхода блока 7, у которых в вычитаемом соответствующие разряды равны нулю.

Сумматор l l позволяет определить в контрольном режиме суммы по модулю два результата .вычитания прямых кодов с выхода блока вычитания 8 и инвертированного результата вычитания инверсных кодов адре- .

40 са с выхода блока 7.

Дополнительный регистр адреса !2 фиксирует в KoHTpoëüíoì режиме результат суммирования с выхода сумматора 11, т.е. адреса неисправной ячейки ОЗУ. Блок выработки сигнала ошибки 13 определяет неисправность адресного тракта ОЗУ.

Оперативное запоминающее устройство может быть подключено к другим устройствам вычислительной системы с помощью внешних шин. 5Î

Оперативное запоминающее устройство работает в следующих режимах: рабочем, контрольном, восстановления информации и определения адреса неисправного элемента.

В рабочем режиме при записи информа1

55 цнн в ОЗ адрес ячейки с контрольным кодом н слово с контрольным кодом, фиксируются соответственно на регистре 1 адреса

4 и регистре 5 слова. Палее адрес и слово поступают в блок контроля 6, гле произволится проверка содержимого регистров и 5 на соответствие контрольным разрялач. Через дешифратор 2 адреса выбирается необходимая ячейка оперативной запоминающей части блока 3 запоминающих матриц и производится запись содержимого регистра 5 в выбранную ячейку ОЗУ. При чтении слово с контрольным кодом из адресуемой ячейки

ОЗЧ блока 3 выбирается на регистр 5 и затем поступает в блок 6 контроля, где проверяется правильность прочитанной информации. В случае искажения содержимого регистра 5 блок 6 выдает сигнал ошибки на шину 22, определяя неисправность ОЗУ. Для определения, где произо:ила ошибка (в информационном или адресном тракте) по сигналу на шине 19 происхолит переключение

ОЗУ в контрольный режим.

В контрольном ре>киче по адресу, сохраняющемуся на регистре от предыдущего обращения к ОЗУ в рабочем режиме, через дешифратор адреса 2 выбирается ячейка

ПЗЧ блока 3, из которой на регистр 5 считывается прямой и инверсный коды адреса ячейки. Прн исправности адресного тракта значения прямого и инверсного кодов адреса на регистре 5 должны соответствовать значениям прямого и инверсного кодов адреса на регистре l. При неисправности адресного тракта обращение производится параллельно в адресуемую ячейку и в ячейку, выбираемую ошибочно из-за отказа дешифратора..Поэтому при чтении информации из

ПЗЧ на регистре 5 происходит наложение содер>кичого действительно и ложно адресуемых ячеек. Определение адреса ложно адресуемой ячейки производится по нижеследующему алгоритму. По управляющему сигналу на шине 19 в блоке вычитания ? производится вычитание из инверсного кода адреса, зафиксированного на регистре 5, инверсного кода того же адреса, хранящегося на регистре 1. В блоке вычитания ? производится вычитание из прямого кода алреса, зафиксированного на регистре 5, прямого кода адреса, хранящегося на регистре l.

Затем разряды разности инверсных кодов адреса с выхода блока 7 ннвертируются элементами 9 НЕ, а те разряды, у которых в вычитаемом соответствующие разряды равны нулю, пропускаются элементами 10 И, на вход сумматора 11 Инверсная разность инверсных кодов складывается по модулн> два в сумматоре 1! с разностью прямых кодов адреса, полученных с выхода блока 8.

Результат сложения (адрес ложно адресуемой ячейки) с выхода сумматора I I поступает на дополнительный регистр 12 и на вход блока ) 3 выработки сигнала ошибки.

Блок 13 выдает сигнал ошибки, определяя неисправность адресного тракта ОЗУ, при этом выдается адрес ложно адресуемой ячейки.

6:.166?8

В режиме восстановления информации определяется истинное значение информации, хранящейся по адресу первого обра-. щения. Для этого адрес ложно адресуемой ячейки с регистра 12 переписывается на регистр 1, содержимое регистра 5 сбрасывается, производится обращение к ОЗУ и и ло>кно адресуемую ячейку записываются нули.

После чего производится повторное считывание информации из действительно адресуемой ячейки. Считанная информация после проверки ее блоком контроля 6 является верной.

В режим определения адреса неисправного элемента устройство переходит по сигналу с выхода блока l3 после восстановления информации. По этому сигналу в бло1(е jj4 сравнения производится сравнение адреса исправной ячейки, храня(цейся в регистре и адреса неисправной ячейки, зафиксированной на р гнстре 12. Блок 14 определяет крайние левые несовпадающие разряды, выдавая в виде единицы сигнал на выходе, соответствующем позиции этого разряда. Этот сигнал поступает в блок 15 определения ступени дешнфратора и на счетный вход одного из триггеров регистра 1 адреса. Таким образом, если крайнимн левыми несовпадающими разрядами являются К-тые разряды, то инвертируется K+1 разряд. Затем производится обращение по полученному адресу к

ПЗЧ и после получения неисправного адреса снова происходит сравнение адресов, хранящихся в регистре адреса 1 и регистре 12.

Если в результате сравнения получено, что крайними левыми несовпадающими разрядами снова являются К-тые разряды, то на выходе блока !5 появляется сигнал, показывающий, что неисправный элемент находится в (К-I)-ой ступени дешифратора. Если же ft р 3óël ã;Iте сря«н fiilн Нс со!!I! л. (ь

+1)-ые разряды, то произ(и!лиг(! и i!- рг.

РО«анне ((+>) Р(331)НДЯ Hclij!!III! .(!i н ."". Ь

И СНОВЯ НР(3Н3730.1И С(3 061! !3 Н(г. Н НС f! i 1,1 j.

Ука:3;3 ни: i!f Я.1i ()1! Hi „: II(»3 f 017101 с:I .I c

Э НОКЯ (IC П!PО«.игit 701;!«7! H(CO«;i;!, .si ;!i(; нм((гнгг(х 1.!i« : i!I!i. 1х((HI(1 cl н I!f;3 . 00»г н

Нра(3730! O ЭЛ(. Мг 7Ы;! (iii170д(.(Н(! C3! C:Н(i!; 7 г

НЫМ Я 17>СС(!."13, лj. «i!ЛН(I!7!C× 73 P(.! (г(! : кОторый (>f!1!c,(cë)f0ã цсиь нснс(г! ;737:(1 мента л(. 07II!13P!IтОРЯЯ, и (3! гг(нь 3".: (!3! 7 .:. i,

36 блока 5, ук;.::ь!:-г Я 7(.,;. f H

Этой цЕ37И IICHC;IV.7:3г..f ..

ИТЯ7(, Пр(-..7(3«;7(л: С г .(Ср«7;-!.-г

МИНЯК3Н(Е(ЪCТрг! Н i НО Л(777(r. !i!

v-ожностнм f!11(зт; н; 7! >! 30»г(r ческii Оирсд(ли ь и:, 010!Iсifc...;j;;f:.;г, гi! г

Крвг НОСТЬ(О дго:.1,!::!C :!! Л .,(г (Н(7(1777Л ic °

p .1у%77Я . ; pÑÌ07ãç((7I,! 007!ОСТ!. c I130!;С, : "..

О г СЮДЯ I I Е O Н 3?((.Н(!i(! Т Ь. (гго >я(«70 няобог гг (!

29 ()(3Е(>ЯТгf«f,0:.-:ЯНОМ ННЯ;(Нисг.

С ЦЕЛЬЮ НОВЬ(!«Ы133Я НЯ (Р;-„ (): ТН (i .."-.:",. !5, оно содерж (г блок сг,авнен73н Язр(: !l(и :: г

ОПРЕДЕЛЕН!333 СТУ г7(. 77И ДЕШИ(.!i! 31 r;13«Я:! .: г. входы блока срЯ7373е(н(я(Я113(со«с .:".":!; -,", ;!

СООтВЕТСТВЕ3(НО С «ЫХОДЯМН РС(ИСГ(гн дополн 3тс.! ьного регист ря ядреся и I!,::.:, выработки сигнЯла Онзн(1!(Ii, ". Вы o;i

ДОПОЛ7333ТС. ЬН! ггг В "О.Р)г3 рс! i. (j г, Cj C i ";:

ЗО ВХОД блока О(77!сд(е.:. Иня стгне}гн (е7«,:, р;:тг: ра адреся соедн;ic!i с в I>().(07! О. Ок, ср:I« нения адресов.

1!сто!7«икн ННФОГ73я7(и 7, ир !ни ГL!c ВО «нг!. мани(. f!pH экс73е13тизе:

l. Л(3!орсков свндетельст«О С(.(,11

35 ¹ 52861:1, кл. Сз 1! С 29/00, 260?,?4

Составитель В. Никифоров РедактоР Э 1 Убииикаи Техреа 0. фуговав корректор С. Щекмар

Заказ 6957/42 Тираж 675 Подписное

ЦНКИПИ Государствеинаго комитета Совета Министров СССР но делам изобретений и открытий! l 3035, Москва, Ж-35, Рауигскэи яаб. ° д 4/5 филиал ППП «Патент», r. Ужгород, ул. Проектная, 4