Преобразователь цифрового кода в аналоговый эквивалент

Иллюстрации

Показать всеРеферат

О П И С А Н И Е !!и ggg7g>

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свил-ву— (22) Заявлено 14. 10.75(21) 2184339/18-21 (51) М, Кл с присоединением заявки №

Н 03 К 13/02

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (23) Приоритет (43) Опубликовано 05. 12.78.Бюллетень Xе45 (53) УДК681.325 (088. 8) (45) Дата опубликования описания 06 д 78 (?2) Авторы изобретения

Б. М. Белоцерковский, И, М. Белоцерковский, В. В. Ольхович и М. Ф. Ярема (71) Заявитель

Б11ЬЛИ1: КА (54) ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В АНАЛОГОВЫЙ

ЭКВИ ВАЛЕНТ

Изобретение относится к области вычислительной и измерительной техники и может быть использовано для преобразования информации из цифровой формы в аналоговую, а также для цифрового управления амплитудными искажениями сигнала произвольной формы.

Известен преобразователь цифрового кода в аналоговый эквивалент, построенный на способе последовательного кусочного воспроизведения зависимости временной функц IH (1) . 1О

Преобразователь содержит блок цифрово1о ввода с подключенными к нему блоками цифровой памяти и цифровой синхронизации и блок аналогового суммирования и сглаживания, соединенный с блоком аналоговых модуляторов.

Недостатком его является наличие фазовых искажений при цифровом управлении амплитудными искажениями аналогового сигнала.

Известен преобразователь цифрового кода в аналоговый эквивалент, содержащий блок цифрового ввода, блок аналоговых величин, блок аналогового суммирования и сглаживания, блок цифровой синхронизации и два тракта цифроаналогового преобразован!1я. Ог)рызова нных олокозl циф1зовой !1а мят!! и олоком аналоговых модуляторов, причем блок цифрового ввода подключен ко входу блока цифровой памяти, блок цифровой памяти и блок аналоговых величин управляют входами блока аналоговых модуляторов, выход которого соединен со входом блока ана IoIoBoI0 суммирования и сглаживания, выход последнего служит выходом устройства (2j.

Недостаток известного устройства — оно не может само по себе осуществлять амплитудные искажения воспроизводимого сигнала, не внося при этом никаких фазовых искажений, то есть не способно производить цифровое управление амплитудами всех гармонических составляющих без нарушения фазовых соотношений между ними. Необходимо отметить, что указанный недостаток вызван Hp составом отдельны. блоков, а построением всей блок-схемы устройства.

Цель предлагаемого изобретения устранение фазовь.х искажений при цифровом управлении амплитудными искажениями аналогового сигнала, воспроизводимого в соответствии с цифровым кодом на

686792 выходе устройства, и расширени(функциональlx Возможностей устройства.

Она;!остигается тем, что, в преобразователь цифрового кода в аналоговый эквивалент, содержа>цнй блок цифрового ввода. блок аналогoabix величин, блок àíà Ioloin>го суммирования H сглаживания, г>лок цифровой cinlxðoíJIB !itèè и äâà тракта цифро;ill2.lol oBoI нре(>бр;<зов <ни)1, сocT()sifft(( каждый из блока цифровой памяти, к выходу которого Ilonключен первый вход блока аналогового модулятора, первый вход ка7кдого блока ц!!фровой памяти подкл!очсн к первому выходу блока цифрового ввода, второй вход каждого блока аналогового модулятора подключен к выходу блока аналоговых величин, выходы блока цифровой синхронизации подключсilBJ к соответствующим Входам каждого блока цифровой памяти и блока аналоговогo мо !улятора, выходы блоков аналоговь<х мо.(уляторов подключены к соответствующим Входам олока аналогового сумчирования и сглаживания, введены блок ,ифрового упреждения и блок цифрового запаздывания, причем второй выход блока цифрового ВВ<>.12 подключен ко входам блоков цифрового уиреж <ения и цифрового запаздывания, выход блока цифрового уг>реждения соеди><ен с третьим входом первого блока цифровой памяти, а выход олока цифрового запаздывания соединен с третьим входом второго блока цифровой памяти.

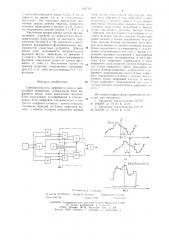

1аким образом, преобразователь цифрового кода в аналоговый эквивалент выполняется íà napaлл(..1ьно-последовательной олок-схеме, вк5цочающей два параллельHûx тракта цифроаналогового преобразования. (ри этом между вторым выходом блока цифрОВОГО ВВОДa Ii Tpcтьим Входом oднОГО из трактов цифроаналогового преобразователя включен блок цифрового упреждения, а между вторым выходом блока цифро!зог(7 ввода и третьим входом другого тракта цифроаналогового преобразования — блок цифрового запаздывания, осуmccTBляющ .е сдвиг временных циклoB работы трактов Ild и --г соответственно. г! 1 <1)и; . Нри()едена ст(эукт pllitsl схе>1(1 ! р()()ораз<я(атсл51, на фиг. 2 — — временll25I ди i Г р !1 >1 (I if, !10 H с ) I Я I01ц а и I! p u I I ц н и P. Г 0 р и б От ы . (:;ема (фиг. 1) содержит блок цифроВого в<1()да, блок 2 аналоговых величин, блок 3 аналогового суммирования и сглаживания, блок 4 цифровой синхронизации, блоки 5 и 6 ци(рровой памяти, блоки 7 и 8 аналоговых модуляторов, блок 9 цифровог<> упреждения и блок 10 цифрового запаз.(ы ва н ия.

Благодаря сдвигу временных циклов работы трактоь на +г и — г соответственно, первыи тракт цифроаналогового преобразователя выраба<ывае упреждающую запаздывающую ступенчатую стр ктуру F (t + т )1<(Обе структуры совергцеHHo идентичны, но

С ТВИН -ГIË Iia 2г:(р3 Г ОТРИ(. HT(., 1ЬНО 3pVI 2.

11(>слс суч3!Нро(>ания в блоке 8 получается структура (1 г =- 1 t — < ) . f (1- — i ), hOT0p25J .3i! I еч ll() (BC pl 2CÒÑH СГ.12Ж и BdHHIO. (.двиг г oi!pcд(ляется число ч S, которое

:3;fiI;)vIIIia(TcsI н блоке 1 и остается неизменныч в Tcчение отрезка времени, кратного йериоду Т = 1„— t(,. Изменяя S, можно акТIIB110 x IipaB. !SIT! формой кр!!Вои (>(1< ().

11окажем, что ступенчатая структура

Г>(1. г ) действител ьно представляет собой амплитудно искаженный сигнал f (t) (какие-либ(> фазовые искажения одного сигна12 по отношению к другому отсутствуют).

Дл5! этого представим f(t) рядом Фурье

1 (t) = Х А„соь qk (t-) (!) °

I ДС fi ООЩЕМ СЛУЧВ(,I<, <.oB <(>„(с) — 4, =- сс»»1., /(Км(+",» Д), к

Тот же сигнал, сд<3:..:,тый и> времени в

Ту Или II II> lO (TU f70fI » !< С -е. 1И l!i ii < С, 32 IIHс ы В а етс 5I (, 1 еду lo щ,; х! Об, ) d з О.;! л (—. «) = P.kCOS yk(t+ T ), 2»

k-c где

<(>к(1 - ) ="(.>;(t =-)<-<р„.(0) = — )(t +Р(Рк®-- х< - = Wk(:) 1;(>, с.>едовате.lbHO, сум.,!а сигналов f (t —, г) и

1" (1 — т, ) дает

/ k

v (t, () = f (t ч с) + (t — .) = Х Л i cos(<((t)

)« ->

-<- ) .7 ??) -(- ?????? ((j>,(Ц вЂ” М>,Z ($

3» 1!Осл(гож;>ест!3ен!1<.!х -,ðèãîíîìåòðè÷åñêèõ

flj)cобра: <)!31<и;!Й из н<>(леднего равенства floлучаеч

О (t, t) = Х А„СОВ Ь),Z СО» <()Z(t) (2)

Видим, о j(-ю гармонику с измененной вО>< = cos kсо()г раз амплитудой, но с неизменной фазой ((7 (1). В частности, примеНЕНИЕ УК2ЗаННЫХ ОПЕРаЦИй (СДВИГа На +г

4» и — — c и п

=Де(,B (t»o, 1 —. (1< (О) j приводит к изчене!<и!о п>лько (13!Ил!Г! < ;(û си! нала в (pi —— — со»<> раз без искажениSI его форчы. Последllc(чожсT быть iicll() 1ьз н<ано для осх»О и(ествления IJ(j>p(!30(j м -.7:I тудной мод\TISIIIHII ГарМÎНИчеCКОГО ("И> !i a, 12.

Выполнение иреобразо вате. IH Iio паралл(льно-и )следовательной блок-cxc3ic (фиг. 1) связано с подкл!Очение3! блоков 9 ii 10 меж Li вторым выходом блока 2 и третьими вхозами блоков 5 и 6. Код числа S по второму выходу блока 1 поступает в блоки 9 и 10, где преобразуется в импульсы, следующие

63!), 92

Формула изобретения

5а(>г.!

Со«тавит«ль 3,. Го.i \ бови !

Риг 2 (?(лактор Б. Павлов ех(оед 0.,1утован 1;оррек(ор 11 Го. сии

Закан б<)б7 4(5 Тира к 1044 !1»лии«но«

ИНИИПИ Государст<3«нного комитета Сов(та Мини«т=ов СССР по делам изобретений и о «;р ь!-, и ! 13033, Москва, Ж-35, Раугискав нао., д. 4/5

Филиал ППП «Патент>о г. Ужгород, ул Проектная, 4 с !я TOT()11 импульсов цикла О,и;кя 4. ПО со сдви п) ч на Время -+ т и -z OT»ncI! Te1I I«)

cIoc. I(. 1HHx. 3TH EIxI !1% 1bcbI ОНРедег!Я юг ВР<.менные циклы работы трактов, например, моменты обращения к блокам 5 и 6, мом IIты открывания ключей блоков 7 и 8 и г. д.

Увеличение аппаратурных затрат при Bblполнении устройств по параллель)ГО-последовательной блок-схеме (в частности, ïî3кл!очение блоков 9 и 10) окупается существенным расширением функциональных возможностей известных устройств. Данные блоки дают возможность воспроизводить функции о(ti т ), зависящие от времени и сдвига T. В частности, можно генерировать функции, зависяшие только от одного арг)мента (t либо c). Отключение одного из трактов позволяет генерировать упреждаюшие f(t + t), либо запаздываюшие 11t — t ) функции.

Г1реобразователь цифрового кода в аналоговый эквивалент, содержаший блок цифрового ввода, блок аналоговых вел ичи н, блок аналогового сучмирования и сглаживания, блок цифровой синхронизации и лвя

25 тракта ш!фроаналогового преобразования, состояшие каждый из блока цифровой памяти, к выходу которого подключен первый

В." ОЛ О." (!! !1 и!i;-i, I() ОВС "0 . 1().!3. 1511 <>П!i, Ii(>РВы и Bx() i каждо ГО б, ".) кя Ii 1l(1)!)< )130! l и. 3! Я1 (!

ПОДЕ. II()H(i!, II«!Ч(0313 13!>IXO 1((> !<)!>Ei Ill! < )Р()ВО! 0 ВВОД !. ВТ(),!ОИ !3ХОД КЯЖ IOI () 0.1 )h;1;IH;1, i()l OB<)! М0,1< ГIЯ ГО )11 ll03(IC IЮ 1< Н К E3blX033

oл0ка я пялоговы х !3сл IHI! I ii, Bb! xoiii! и. IOI

:!Пфровои синхроппзil!ll!!I иодк,1к)чены к соОтвеTcTB(IOI!!I!xi в. о 1Hì каждого блока цпфРОНОЙ Пcl 31 ЯТИ !! 0.10Kа <111?1,10ГОБОГО Xi 0.l), I иТОра, i3bl X()3bi 0.10ков я Н21,10ГOBb!X мо iz. l ЯТОров подкл!очены к соотвстствуюц(им Bxo;Iiix!

Олока аНаГIОГОВОГО CX XI XIHpOBBH II51 I! сГл!IЖПвания, от.!ича>ои(и(,09 тем. что, с целью усгранения фазовых искажений и расшире111151 функц!н)нальных возможностей, в HOIO введены Олок цифрОВОГО х прежде!3ия и О 101> цифрового запа 33! !ванин> причеч второй ныхо3. олока цифрового вво 1я 1103 кл!очеи кс (3ходам блоков цифрового упреждения и Li!.фрового запаздывания, Bb!xoil, блок;1;1:(фр,— вого упреждения соединен с Грет Нх вхо:1

Пер ВОГО О.IОKH цифрОВОй Па м 511 li, я !3 I>!X()g блока цифрового запаздывания со«.1,;пс!! с

: рстьим вхо(ом второго блока циф1)0!30й 1;1 и Ii

Источники информации, принятые Во!3!!!1х!(П!ИЕ IIÐÈ ЭКСПЕРТИЗЕ:

l. Авторское сви 1етельство СССР

Л"в -108339, к,!. Н 03 K 13 0 ). ). Авторское свидетельство СССР

>кГв 385)98, кл. И 03 1, 13 03.