Устройство для мажоритарного декодирования

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сеюа Сфветскмк

Соцмапмстмчасимк

Респубпми ()636806 (63} Лополнительное к авт. свид-ву (22) Заявлено 240974 (2l) 2064968/18-09 с присоединением заявки № (М} N. Кл.

Н 03 К 13/32

Н 04 1, 1/10

Государственный комитет

Совета Министров СССР йо делан изобретений и открытий (23) Приоритет (43} Опубликовано 05.12.78. Бюллетень ¹ 4 5 (45) Лата опубликования описания 05.1278 (53) УЛК 621 . 39 4 . 14 (088. 8) f к

В. В. Гулевский, В. А. Семенов и Г,. Г.:.Степчейкова (72} Авторы изобретения (73) Заявитель (54) УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО

ДЕКОДИРОВАНИЯ

Изобретение относится к декодирующим устройствам и может быть использовано в системах передачи данных и вычислительной технике для коррекции ошибок. 5

Известно устройство для мажоритарного декодирования, содержащее объединенные по входу пуск накопитель искаженных слов и блок управления, выходы которых подключены к соответствующим входам распределителя, а также элемент И и выходной накопитель

И.

Однако известное устройство имеет низкую помехоустойчивость.

Целью изобретения является повышение помехоустойчивости.

Для этого в устройство для мажоритарного декодирования, содержащее объединенные по входу пуск накопитель искаженных слов и блок управления, выходы которых подключены к соответствующим входам распределителя, а также элемент И и выходной накопитель, введены счетчик, коммутатор, триггер и декодер. При этом выходы распределителя через последовательно соединенные счетчик и коммутатор подключены к одному из входов триггера, выход которого подключен ко входу выходного накопителя через последовательно соедиченные элемент И и декодер, соответствующий выход которого подключен к управляющим входам накопителя искаженных слов и блока управления. Дополнительные выходы блока подключены к соответствующим входам накопителя искаженных слов и коммутатора, причем на управляющий вход счетчика и на другой вход триггера поданы сигналы установки исходного состояния, а на управляющий вход распределителя и на другой вход элемента

И поданы тактовые импульсы.

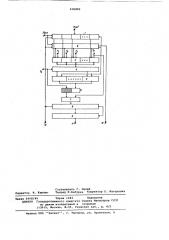

Структурная схема устройства для мажоритарного декодирования представлена на чертеже.

Устройство для мажоритарного декодирования содержит объединенные по входу ™пуск накопитель 1 искаженных слов и блок управления 2, выходы которых подключены к соответствующим входам распределителя 3, счетчик 4, коммутатор 5, триггер б, элемент И

7, декодер 8 и выходной накопитель 9.

Выходы распределителя 3 через последовательно соединенные счетчик 4 н коммутатор 5 подключены к одному из ,входов триггера б, выход которого подключен к входу выходного накопитеб 36800

Я ля 9 через по(..ледовательно соедих}енные элемент И Г и декОдер 8 . СООтаетств>щ»i Й Быхо }Г> дс кодера подкл}Очен к

v lips I B j !f1!B!3 (} f м и:"-:ДQj> >ww>} ц а }(О пит ("ля 1 искаженныхх схIса и блОка >}4}раалеция 2, дополни .Г}ель(}ые ВыхОды которого ЛОд

K Г1(() ЧС Н Ы K, OO T а>," >" С т а У ЮЩ3} }ГГ а > Ода }>Г Н акОпцтеля if кГО!}ГГ>}утГэ>тора 5. Иа упраВляющий 3)хГ)>(c t)>;-:-;.>) ч>)к а 4 и на .> 4 О угой ВХОД трнг>. cpi () поданы сигналы установки

}ус)(О(хчогo cQcòîÿ>1}>(я а на Г)>прааляю

}Г}3}йГ вход расп()е>д(>4лителя 3 и на другои I(Î вход злеГ>е}}т Гч И поданы тактовые импульсы.

Бакопитех(ь 1 искаженных слов обеспечива т а}i (с1>, х})анен}}е H c(IHTb}Bание 4-) }} б)Г.ГТ где Д вЂ” ОДГ}оих}енные 445 искажен(>ы: и "разрядцые слОааГ посту па}Г)((ке !! а а}(О}(YOTpo>(GTB4 со скоростью

В > 3-(п>ноь »! ft IГ (х>"Г>» j}>!i g ца!; lпцT(> чь 4(с"

К а)}(Е}! !41!Х СЛ(> а }>(QKC T 1(PO}!BBQg(H L Г) С }1 ()ЦГТЦМ>Ц. ГЛИ СХ}(ГВ-! Г(H . 4".j!OB q (Г); + С ), Г}(ТО1) ОЬ1}}БКЦ З:JIG! e ° Сх}ОВД; 3:)П}(са}-1-»

>ГГ.,>Е ..., >It> \(. >.". Г}:РЕГ}3> >}C "t!,>>,i. ННЫХ C!IQ!t i Г. tH!i" т}>Г:, „I Г-.т Я со (IГ>>ро>ст) !() В D Одновре-"

МЕЦЦО Ц t-i!!!KP!->ЦЦО 1}а>Ц(ная ПЕРВЫК, ..Ф

14(а .>»Я Ч>-,:а . I,>Ч>}>> Тын а ЦЦЕ Н>ГГГ)ОР}1(1ЦИИ С

4(я(ГО)}((> (>Г}Я;Г(3>а)4(е!";}} >:: > ЛГ)н }(ро}Гаво>(14 Г ся = }) (-,.г-:.. Нера(>хне й, Вико!> .;". 1}а ко 41}> т ех(х!

1 ис}(а>же}»>} ",». ОГ}оа с(хсдицецы CG Вхо." дами раcòpå!-.å.r! I!Tt-"..J}ë ."> Г состоящего, У:;-.;"(.> Ц }.Г»Г}>Г(3 Г ПС>ст>ГГ}аЕ Г С)}Гнал, к>)то >j>4!f y!JTti If ä B j!!f! Г>}>>х>>(!3 тель 1

H(;,"Ка)Г>(ЕГ}ЦЫ".". (,. .i!t)B а Р;- ГГ}1Р>1 С !i! }b}BаЦИЯ да)> (>} })I 11 зацу,- i(;4(>J}! }I(i>i(уп() 11>11}p(}}f f(2, 85 упоааляккацй а}(ОЛ с 1Г i >f,fка 4} со скорост }o B с т:..> .To!,. "(,, }()(:(ЦГ}аg.!> О>иг«-.

Цал, }(()ТГЭ})Г>йГ Устаиаа)1}(а:}Г>)> (>4}(.: } >(Г(((4 "i ТР}ггер () I чсх.)дцо (>(T(4}f}(3 е

Влек уцрау..Пения (Г>ЗВ>М}}()уа.} Г*}(Г>}ГГ}Г,}3 от}(аза > - >т де}(4)ди})онациЯ i .С пополни

ТГ>х}ьнГ> > O B}-,!"- Г)!t"; "-> i Qi-Q (IJ!ii!(4) поступает цд а}Г)(Г)д уст(>()((стан и

ВХОД H акО}}ит<ГЯ)» ИС „>4,(" >! !}hI)(Г ЛОВ .Г 14

1)ааля 1 p(> ()()>} (>}(}Г > 2! ",}Г>;ГТ>)> I (> ) )ГГ 5 и р Г }С". прсделцтеля

В)}ОГ(упрt)»»}II} Я o>ið(I ц>Г(ц> 4 4 IT и >>H

-* }>

Х(Е}(О(33!Рг)ГЗ>",Ii«>! : - .> ., С;, Н-}I,>11>4;}TO}j ИСГ f Г>

ПРСГЬ)(>. Ц,>I . i t 4ЦНГ}3> Г. Г . (((g ° (ГОЛО

Сл()а УГ(а> (Г "„>I> IIH (а >I> >t>орк>"> I

Jl„ I! ЧГ};.>Г) >}> (>". .}(i Я Г >а („, (Г}i » >ДЕ Г(и "4 (}ХГ>ЗМ >)О

Ца аы}(ОДГ}). i;.;" >Га,ГГ(4);:>!I!it-,хц}я >()Q}1(>Г}}ру}ГГТЯ }}QC j}4=. ГГ(>а а Т (> i}}>!}(> (., >ГЯ Г,"„;*" () тt>}f 4) / }Г

4((>}>}ДЦ>ЧГ> Kа>кда }(rt ГГ(У4, (.1)i Г)(""">Г"тоит

Hз Q разрГГДОВ „цэ }(О Г.О})ых j, (1((((-j)

7> 5 > 8 Г> --1 - ч>= ". Яo=.;:) p;!:-:}JI}T}ciâ едцци-.: 55

4 >ы В i: > -;-:o (Q;, },-4 ц >Г,," >, Г> >) Г) )> >I- 4 Г О c T ь ацл),НО1-(- 1;...-;Цра;, леГ}}}я сх}()а;} прц ((!IQ

}Гь}1 ка)((У(Г)ем}(т (.".Я к 1 .. (»!(Г цраах}ецц Я

}(О}.-»}утато}ро}(-, по Од}!Ому из ДО110лцн(ел. -., }}ы--- 4(>!)(о(}>О }>3 бло (; а у }(1)а}>)}Г >1!1}Я 2 @

44О}1а} .>то>! (Цгцалы 1}а4 ВХОД Одной нз схем И кОГ>}м )та тора 5 > Перв}>14 1 всегда фОР(1(4P>/>ТCЯ Г И(>наЛГ ПОСГ4>>I!H!((4!HÉ Hа

1)о сх}(д}1} }4)}() с. м у И . Управляющие с и г-ца выходах блока упраВлецня 2

COO T }i t > T C T )3 jil0 T

Счетчик 4 предназначен для подсчета числа сигналов, соответствующих 1, поступающих с выхода распределитех}я 3. Счетчик выполнен в виде (0 + 2 ) — разрядного регистра сдвига. Выходы разрядов с 3-го до (Е+2) соединены соответственно с 0 входами коммутатора 5.

Йо К шинам с выхода блока управления 2 на вход коммутатора 5 поступают уп}равляющие сигналы. Коммутатор

5 обеспечивает подачу единичных сигналов с выходов счетчика 4 на вход триггера б. Если число сигналов, поступивших с выходов распределителя

3 на,вход счетчика 4 3 Р, то на вход триггера б поступает сигнал, соответствующий 1 . Коммутатор 5 содержит }) схем И. Выходы коммутатора соединены с правым плечом триггера >

Распределитель 3 содержит d схем

И и обеспечивает преобразование д разрядны)< комбинаций, постуПаЮщик на его входы с выходов накопителя 1 искаженных слов с частотой В1 s последовательные, которые поступают на вход счетчика 4 сО скОрОстью В "- В.((8 + 1 )

11а входы схем И распределителя поступают одновременно д сигналов с выходов накопителя искаженных слов, единичных сигнах(ов с блока управ)IQff!IH и тактовые сигналы }, + т„.

Если все три сигнала на входах схем И распределителя соответствуют-„ единице, То на выходах схем И также

Формируется сигнал, соответствующий l . Выходы схем И распределителя

3 соединены со входом счетчика 4. Эти сигналы используются как тактовые для счетчика.

Триггер б обеспечивает запоминание сигналов, поступающих с коммутатора 5, Выход левого плеча триггера соединен со входом элемента И 7.

Элемент И 7 обеспечивает подачу ца вход декодера 8 сигналов со скоростью В(а моме}(т действия такта

7< . Выход элемента И 7 соединен со входам декодера 8. Вход, на который }(осту}1ает тактовый сигнал Т (1, сое-

Дпцец cQ BTGpb>м ВЛОДОм элемента И 7 >

Декодер 8 служит для проверки правильности исправления слов после мажоритарного декодирования. Один выход декодера 8, по которому поступают инф01)}Г(а}1}1онн}яе сигналы соединен со анодом выходного накопитех1Я 9. Другой выход, по которому поступает сигнал об Отсутстаци ошибок в слове, соедицац с накопителем 1 искаженных слов, . блОКОм )>Ù2ÂÐJfeH}f ß 2 и ВыхОдОм устройстВа Третий выход, пО кОторОму пОсту пает сигнал О наличии ошибок в слове, с(зех(н}(е}} с Выходным накопителем 9 для его Очистки и установки в исходное

СОСТОЯНИЕ.

Вы)(од}(о(} накопитель 9 исключает возможность выдачи потребителю слова

5 б 3680 с обнаруженными декодером S ошибками.

Выход накопителя 9 соединен с инфор- мационным выходом устройства.

Предложенное устройство работает следующим образом.

Искаженные слова с входа устройства записываются в накопитель искаженных слов 1. Затем сигналами, поступающими с входов пуск и Тр производится установка накопителя 1 искаженных слов в режим считывания данных, запуск блока управления 2 и установка счетчика 4 и триггера 6 10 в исходное состояние, после чего сигналом, поступающим с блока управления

2 на вход коммутатора 5, подготавли- вается к работе одна иэ схем И коммутатора. На эту схему по соответствую- 15 щему входу поступает сигнал, соответствующий единице, одновременно первые разряды всех Д слов (например, 11101) с накопителя искаженных слов и д -разрядная команда с.блока управления, содержащая Х единиц (lllll), поступают на входы схем И распределителя. Стробирующие импульсы Т„ †: Т, начинают опрос схем распределителя.

Сигналы с выходов этих схем, соответствующие 1, производят продвижение 1 в счетчике 4. Если число таких сигналов будет > t. (в примере 4 5, С = 3), то сигнал соответствующий 1, с выхода счетчика через коммутатор 5, поступит на триггер б и изменит.его состояние. Стробирующий сигнал Тя разрешает прохождение сигнала с выхода триггера 6 через элемент

И 7 на вход декодера 8, с выхода которого этот сигнал поступает на вход выходного накопителя 9. Затем счетчик 4 и триггер б сигналом То устанавливаются в исходное состояние.

Одновременно на входы распределителя

3 поступают вторые разряды слов с 40 накопителя 1 искаженных слов и т.д.

Если после считывания и разрядов декодер 8 не обнаружит искажений в слове, то на его выходе формируется сигнал, который поступает на выход

10 устройства и входы накопителя 1 искаженных слов и блока управленйя 2 для установки их в исходное состояние.

Исправленное слово с накопителя 9 поступает на выход 11 устройства.

При обнаружении ошибок в слове, на выходе декодера 8 формируется сигнал, который поступает на вход выходного накопителя 9 для его очистки и установки в исходное состояние, после чего на выходах блока Управления

2 формируется новая команда н производится попытка исправления слова путем анализа нового сочетания искаженных слов.

Если после анализа всех Н возможных вариантов исправления слова не происходит, то на выходе блока управления

2 формируется сигнал отказа от декодирования, который поступает на выход

12 устройства и вход накопителя 1 искаженных слов для его установки в исходное состояние.

Предложенное устройство имеет повышенную помехоустойчивость за счет увеличения числа попыток исправления.

Формула изобретения

Устройство для:мажоритарного декодирования, содержащее объединенные по входу пуск накопитель искаженных слов и блок управления, выходы которых подключены к соответствующим входам распределителя, а также элемент И и выходной накопитель, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены счетчик, коммутатор, триггер и декодер, при этом выходы распределителя через последовательно соединенные счетчик и коммутатор подключены к одному нз входов триггера, выход которого подключеН ко входу выходного накопителя через последовательно соединенные элемент И н декодер, соответствующий выход которого подключен к управляющим входам накопителя искаженных слон и блока управления, дополнительные выходы которого подключены к соответствующим входам накопителя искаженных слов и коммутатора, причем на управляющий вход счетчика и на другой вход триггера поданы сигналы установки исходного состояния,, а на управляющий вход распределителя и на другой вход элемента И поданы тактовые импульсы.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

9 387521, кл. Н 03 К 13/32, 1971.

636800

Якая

Составитель Г. Челей

Техред Н.Бабурка Корректор П. Макаревич

Редактор; И. Карпас

1 филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Заказ 69б8/49 ТМРаж 1044 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР

flD делаи изобретений и открьпий

3.13035, Москва, X-35„ Раушская наб., д. 4/5