Устройство выдержки времени

Иллюстрации

Показать всеРеферат

(ii) 636801

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИТИЛЬСТВУ (61) Дополнительное к авт. свиа-вуСоюз Советских

Социаяистииеских

Республик (51) М. Кл.

Н 03К 17/28 (22) Заявлено 13.09.76 (21)2403643/18-2 с присоединением заявки №

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (23) Приоритет

t (43} Опубликовано 05.12.78 Бюллетень №4 (53) удК 621.318.57 (088.8) (45} Дата опубликования описания О5.12.78

И. Л. Калюжнер, В. Ф. Костопонов, Ю. С.серпик, Л, И. Симон и В. A. Якимов (72} Авторы изобретения (71} Заявитель

Одесский филиал Всесоюзного института по проектиро энергетического строительства "Оргэнергострой нию орга ййэйес

- („ )(Щ и ! Ь(Ф f/ !

1 (54-}, УСТРОЙСТВО ВЫДЕРЖКИ ВРЕЯЕНИ

Изобретенйе относится к области импульсной техники и автоматики, Известны устройства, содержащие входной транзистор, база которого соеди» нека с входом устройства и через рези- 5 стор - с минусовой шиной источника питания, эмиттер соединен с земляной шиной, а коллектор через резистор - с плюсовой шиной источника питания; выходной транзистор, база которого через резистор соединена с плюсовой шиной источника питания, эмиттер - с земляной шиной, а коллектор - с выходом устройства и через резистор - с плюсовой шиной источника питания, конденсатор, МОП-транзистор, ди- 15 оды, резисторы и транзистор нуль-индикатора, при этом конденсатор одной обкладкой соединен с затвором МОП»транзистора, че- рез диод с коллектором входного транзистора, а через резистор - с плюсовой ши- 20 ной источника питания, другой обкладкой соединен со còoêoì МОП-транзистора и с цепью, состоящей из параллельно включенных диода и двух. последовательно с0» единенных резисторов, к средней точке 25

2 которых подключена база транзистора нульиндикатора, эмиттер которого через диод подключен к минусовой шине источника питания, а коллектор соединен с базой вводного транзистора, исток МОП-транзи» стора подключен к плюсовой шине иск рника питания f1), !

Указанные устройства имеют недостаточную стабильность выдержек времени, Известны также устройства, содержащие токозадающую цепь, МОП-транзистор, времязадающий конденсатор, усилитель, эмиь терный повторитель (2).

Цель изобретения - повышение стабильности выдержки времени.

Для достижения цели в устройстве, содержащем токозадающую цепь, подключен- ную к затвору МОП транзистора и к одной из обкладок времяэадающего конденсатора, усилитель, вход которого подключен к стоку МОП-транзистора, истоком соединенного с источником напряжения смеще-" ния и эмиттерный повторитель, выход усилителя через эмиттерный повторитель соединен с второй обкладкой конденсатора.

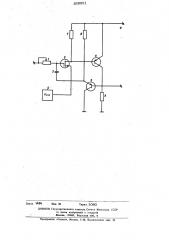

На чертеже представлена принципиальйая схема предлагаемого устройства.

Устройство содержит токозадающую цепь, выполненную, например, в виде резистора

1, МОП-транзистор 2, времязадающий кон- 5 денсатор 3, усилитель на транзисторе 4, источник 5 напряжения смещения, эмиттерный повторитель на транзисторе 6, резисторы 7-9.

Устройство работает следующим обра- 1О зом

В начальный момент времени конденсатор 3 разряжен и МОП-транзистор 2 заперт напряжением источника 5 смещения.

Закрытое состояние транзистора 4 обеспечивается малым сопротивлеиием резистора

7. При этом транзистор 6 открыт отрицательным потенциалом относительно эмиттера, подаваемым через резистор 9, При подаче напряжения с фиксированным уровнем на резистор 1 конденсатор 3 заряжается через резистор 1 и открытый: транзистор 6. Через некоторое время, обу словленное величиной постоянной времени времязадающей цепи и величиной напряжения смещения, напряжение на конденсаторе

3 превысит напряжение смещения и транзистор 2 начнет открываться, открывая при этом транзистор 4. Потенциал на базе транзистора 6 возрастает, закрывая его," и возросший потенциал на эмиттере транзистора 6 через времязадающий конденсатор 3 передается на затвор МОП-транзи. стора 2, еще более открывая его. Воэника35 ет лавинообразный процесс, открывающий транзисторы 2 и 4 и закрывающий транзистор 6. При этом на выходе устройства (на коллекторе транзистора 4) появляется сигнал. При снятии сигнала с входа устройства, сигнал на выходе пропадает, так как напряжение на конденсаторе 3 стало мень4 ше напряжения смешения.

Длительность выдержки времени определяется величиной тока заряда конденсатора.

3 и его емкостью, а также величиной напряжения смещения. Изменением любой из этих величин можно регулировать выдержку времени. Однако наибольший диапазон изменений выдержек времени, может быть достигнут изменением тока заряда конденсатора 3. Так, например, если токозадающая цепь будет в простейшем случае выполнена в виде резистора 1, то диапазон выдержек времени будет определяться диапазоном возможных значений этого резистора, нижняя граница которого лежит в пределах сотен Ом, а верхняя определяется входным сопротивлением МОП- транзистора, достигающим величины 1015 Ом и сопротивлением утечки конденсатора, которое может

9 10 достигать 10 -10 Ом.

Формула изобретения

Устройство выдержки времени, содержащее токозадающую цепь, подключенную к затвору МОП-транзистора и к одной иэ обкладок времязадающего конденсатора, усилитель, вход которого подключен к стоку МОП-транзистора, истоком соединенного с источником напряжения смещения, и эмиттерный повторитель, о т л и ч а ющ е е с я тем, что, с целью повышения стабильности выдержки времени, выход усилителя через эмиттерный повторитель соединен с второй обкладкой конденсатора, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СС Р

¹ 479170, кл. Н 01Н 47/18, 14.12.72.

2. Журнал "Приборы и системы упрац ления", № 6, 1972, с. 50-51 (прототип).

@36801

Заказ М94 йзд. И Тираж 1060

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открцтий

Москва, 113035, Раушская наб., 4

Предприятие кПатент», Москва, Г-59, Бережковская наб.. 24