Интегральный логический элемент для возбуждений линий передачи коллективного пользования

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6t) Дополнительное к авт. санд-ву (22) Заявлено 290574 (23) 2032172/18-21 е присоединением заявки Ю (23) Приоритет (43) Опубликовано 051278. Бюллетень ¹ 45 (45) Дата опубликования описания 05.1278

Саюа Соаетскнк

С щиакистически и

Республик

1 (51) М. Кл.

Н 03 К 19/08

Государственный комитет

Соеета Министров СССР по делам изобретений н открытн и (БЗ) УДК 881. 325. .63 (088.8) ., ° -а

1

У

8 И. Долкарт, Г. Х. Новик, В.Н. Степанов и С. Ф. Редина

Ъ (72) Авторы изобретения (7!) Заявитель (54) ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕИЕНТ

ДЛЯ ВОЭБУЖДЕНИЯ ЛИНИЙ ПЕРЕДАЧИ

КОЛЛЕКТИВНОГО ПОЛЬЗОВАНИЯ

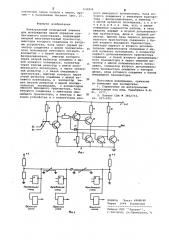

Изобретение относится к вычислитеЛьной технике, в частности для перЕдачи быстродействующих сигналов по . линиям передачи коллективного поль-. зования в системах, использующих интегральные схемы транзисторно-транзисторной логики (ТТЛ) .

Известен обычный клапан серии

131, включающий входной многоэмиттерный транзистор, фазорасщепитель, смещающий транзистор, нижний и верхний выходные транзисторы (1) .

Недостаток этого устройства — малая нагрузочная способность (обеспе" чивает ток менее 0,5 мА), однако, при увеличении нагруэочнОЙ способнос-. ти за счет уменьшения величины резистора в коллекторе выходного транзистора увеличивается ток короткого за- @ мыкания, что приводит к увеличению рассеиваемой элементом мощности и к разрушению элемента.

Известен логический интегральный элемент для возбуждения длинных линий (21, содержащий узел защиты от коротких замыканий, содержащий два транзистора и обеспечивающий ограничение выходного тока при коротком замыкании.

Недостаток =-лемента состоит В том, что в состоянии, когда несколько элементов, подключе ;ных к линии коллективного пользования находятся в состоянии логической единицы (лог. единицы ), а одиH — в состоянии логического нуля (лог, нуля ), элемент, находящийся в состоянии лог. нуля, может быть разрушен.

Известна интегральная схема трехуровневого элемента, в котором к уровням лог. нуля и лог. единицы добавлен уровень выключения, когда выключены верхний и нижний выходные транзисторы. Третий уровень устанавливается сигналом контроль по специальному входу. этот сигнал включает схему на -рех транзисторах„ которая подает низкий потенциал на базу смещающегс транзистора и запирающий смещающий и верхний выхОднОй ТранзистОры.

Недостатком известной схемы является возможность выхода ее из строя при длительном включении второй схемы, ПОДСОЕДИНЕННОЙ К ЛИНИИ пользования, выходной сигнал которой имеет значение, противоположное значению выходного сигнала первой микросхемы. При этом будет рассеивать,ся недопустимая мощность верхним вы