Адаптивный корректор сигналов фазовой модуляции

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (63) Дополнительное к авт. санд-ву (22} Зайвлено260576 (21) 2364873/18-09 с присоединением заявки РЙ о 636807 (5f) N. Кл.

Н 04 В 3/04

Государственный комитет

Совета Министров СССР но делан нзобретеннй и открытн Й

{23) Приоритет (5З) УДК 621. 391, .822.4 (088.8) (43) Опубликовано 0512,78. Вюллетень р6! 45 (45) Дата опубликования описания 05.1278 (72) Авторы изобретении

С.A. Курицын, B. Ã. Гри горьев, Э. П.,Перфильев, . и В.Х. Афанасьев

t г

Ленинградский электротехнический инстьРгу "связи им. проф. М.А. Бонч-Бруевича

Pl) Заявитель (54) АДАПТИВННИ КОРРЕКТОР СИГНАЛОВ фАЗОВОИ МОДУЛЯЦИИ

Изобретение относится к электросвязи и может использоваться в системах передачи данных с фаэовой и относительной фазовой модуляцией.

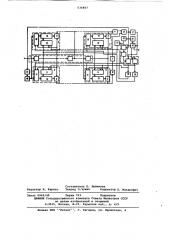

Известен адаптивный корректор сигналов фазовой модуляции, содержащий блок задержки, каждый из П выходов которого через соответствующий иэ и аттенюаторов синфаэного подканала подключен к одному иэ П входов первого сумматора, а через соответствующий из П аттенюаторов квадратурного подканала каждый иэ П выходов блока задержки подключен к одному иэ дт входов второго сумматора, выход которого через фаэовращатель подключен к первому входу третьего сумматора, второй вход которого соединен с выходом первого сумматора, а выход третьего сумматора подключен ко входу блока выделения тактового колебания и к первому .входу детектора, второй вход которого соединен с выходом блока выделения тактового колебания (1) .

Однако известный адаптивный корректор требует затраты значительного времени коррекции вследствие недостаточной скорости сходимости алгоритма адаптивной настройки. цель изобретения — сокращение времени коррекции путем повышения скорости сходимости алгоритма адаптивной настройки. для этого и адаптивный корректор сигналов фаэовой модуляции, содержащий блок задержки, каждый иэ П выходов которого через соответствующий из и аттенюаторов синфазного подканала подключен к одному из П,входов первого сумматора, а через соответствующий иэ П аттенюаторов квадратурного подканала каждый иэ tl выходов блока задержки подключен к одному иэ П входов второго сумматора, выход которого через фаэовращатель подключен к первому входу третьего сумматора, второй вход которого соединен с выходом первого сумматора, а выход третьего сумматора подключен ко входу блока выделения тактового колебания и к первому входу детектора, второй вход которого соединен с выходом блока выделения тактового колебания, введены: П синусных конверторов, П косинусных конверторов и 2 П усреднителей; первый и второй выпрямители, первый и второй фильтры нижних частот; первый и второй блоки сдвига импульсов, блок формирования стробнрующих импульсов и блок выделе