Измеритель краевых искажений дискретных сигналов

Иллюстрации

Показать всеРеферат

Сеюз Советскнк

Сецнелистнческик

Республик

ОПИСАИИЕ „„

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное к авт. свид-ву(22) Заявлено 180177 (И) 2445220/18-09 с присоединением заявки М (23) Приоритет (43) Опубликовано 051278. Бюллетень ¹ 45 (45) Дата опубликования описания 10.1278 (5t) И. Ил.

Н 04, 11/08

Государственный комитет

Совета Министров СССР но делам изобретений и открытий (53) УДМ

621.391.832. . 44 (088. 8) (72) Авторы изобретения

Ю. И. Пискун и Ю. И. Попше

P3) Заявитель (54 ) ИЗМЕРИТЕЛЬ КРАЕВЫХ ИСКАЖЕНИЯ ДИСКРЕТНЫХ

СИГНАЛОВ

Изобретение относится к технике передачи дискретной информации и может использоваться, например, в электроизмерительной аппаратуре телеграфной сети.

Известен измеритель краевых искажений дискретных сигналов, содержащий последовательно соединенные блок согласования и фазовый дискриминатор, второй вход которого соединен с его первым входом через блок формирования идеальных значащих моментов восстановления, второй вход которого соединен с выходом генератора, а также блок установки режимов и блок памяти fl) .

Однако известный измеритель краевых искажений дискретных сигналов имеет невысокую точность.

Целью изобретения является повышение точности измерений.

Для этого в измеритель краевых искажений дискретных сигналов, содержащий последовательно соединенные блок согласования и фазовый дискриминатор, второй вход которого соединен с его первым входом через блок Формирования идеальных значащих моментов восстановления, второй вход которого соединен с выходом генератора, а также блок установки режимов и блок памяти, введены первый и второй триггеры, первый и второй элементы И, блок счета, дешифратор и блок сравнения. При этом выход блока формирования идеальных значащих моментов восстановления подключен к первому и второму входам первого триггера,к первому входу второго триггера„к первому входу первого элемента И и к первому входу блока счета, второй вход которого соединен с третьим входом первого триггера и первым выходом фазового дискриминатора. Второй выход последнего подключен к четвертому входу первого триггера,ко второму входу второго триггера и к первому входу второго элемента И, второй вход которого соединен со вторым входом первого элемента И и с выходом второго триггера. Третий вход второго триггера соединен с первым выходом блока установки режимов, второй, третий и четвертый выходы которого подключены соответственно к третьему входу первого элемента И, к третьему входу второго элемента И и к первому входу блока памяти. Второй, третий и чет вертый входы блока памяти соединены соответственно с вьвсодом второго эле» мента И, с выходом первого элемента

8 (636814

И и с выходом блока счета, третий и четвертый входы которого соединены соответственно с выходом первого триггера и с ныходом генератора. Выход блока памяти подключен ко входу дешифратора и к первому входу блока сравнения, второй вход которого соединен с выходом блока счета, а выход блока сравнения подключен к четвертому входу второго триггера.

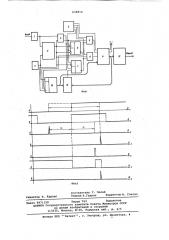

На фиг. 1 представлена структурная схема предложенного устройства; на фиг. 2 — временные диаграммы, поясняющие его работу.

Выход блока 3 формирования идеальных значащих моментов восстановления подключен к первому и второму входам первого триггера 6, к первому входу второго триггера 7, к первому входу первого элемента И 8 и к первому входу блока счета 10, второй вход которого соединен с третьим входом первого триггера 6 и с первым выходом фазового дискриминатора 2. Второй выход дискриминатора подключен к четвертому входу первого триггера 6, ко второму нходу второго триггера 7 и к пер-40 ному входу второго элемента И 9, второй вход которого соединен со вторым входом первого элемента И 8 и с выходом второго триггера 7. Третий вход триггера 7 соединен с первым выходом блока установки ре>кимон 5, второй, третий и четвертый выходы которого подключены соответственно к третьему входу первого элемента И 8, к третьему входу второго элемента И 9 и к первому входу блока памяти 11. Второй, третий и четвертый входы блока памяти

1l соединены соответственно с выходом второго элемента И 9, с выходом первого элемента И 8 и с выходом блока счета 10, третий и четвертый входы ко- торого соединены соответственно с выходом первого триггера 6 и с выходом генератора 4.

Выход блока памяти 11 подключен ко входу дешифратора 12 и к первому 60 входу блока сравнения 13, второй вход которого соединен с выходом блока счета 10, а выход блока сравнения 13 подключен к четвертому входу второго триггера 7. 65.Измеритель краевых искажений дискретных сигналов содержит последова- 15 тельно соединенные блок согласования

1 и фазовый дискриминатор 2, второй вход которого соединен с его первым входом через блок 3 формирования идеальных значащих моментов носстанонле- 20 ния. Второй вход блока 3 соединен с выходом генератора 4. Измеритель также содержит блок 5 установки режимов, первый и второй триггеры 6 и 7, первый и второй элементы И 8 и 9, блок счета 10, блок памяти 11, дешифратор

12 и блок сравнения 13.

Измеритель краевых искажений дискретных сигналов работает следующим образом.

С выхода блока согласования l сигнал (фиг. 2,а) поступает на вход блока формирования идеальных значащих моментов восстановления 3, и по отрицательному перепаду сигнала с его выхода (фиг. 2,б) первый триггер 6 сбрасывается н состояние О, а сигналом с его нулевого выхода блок счета

10 удерживается в состоянии 00.....00 . При наличии отрицательных искажений сигналом с первого выхода фазового дискриминатора 2 (фиг.

2,н) триггер 6 устанавливается н состояние 1, а блок счета 10 сбрасывается н состояние 0 и начинает считать импульсы генератора 4.

В режиме измерения индивидуальных искажений второй триггер 7 сигналом с выхода блока установки режимов 5 удерживается в состоянии 0 . Элементы И 8 и 9 по входам, связанным с нулевым выходом второго триггера 7, оказываются разрешены, а потому по сигналу с выхода элемента И 8, начало которого совпадает с положительным перепадом напряжения на выходе блока формирования идеальных значащих моментов восстановления 3, в блок памяти 11 перезаписывается содержимое блока счета 10, соотнетствующее величине отрицательного искажения. Выход блока 11 связан с дешифратором 12, выход которого соединяется непосредственно, например, с соответствующими электродами цифровых ламп.

В зоне измерения положительных искажений положительным перепадом сигнала с выхода блока формирования идеальных значащих моментов восстанонления 3 перный триггер 6 устанавливается н состояние 1, блок счета 10 начинает счет и при наличии искажения импульсом со второго выхода фазового дискриминатора 2 (фиг. 2,г) через элемент И 9 содержимое блока счета 10, соответствующее величине положительного искажения, перезаписывается н блок памяти 11. Этим же сигналом сбрасывается в состояние 0 первый триггер 6.

Сигналы с выходов блока установки режимов 5, поступающие на входы элементов И 8 и 9, позволяют задавать режимы измерения краевых искажений: положительных и отрицательных (разрешены оба элемента И), только положительных (запрещен И 8, разрешен И 9) и только отрицательных (запрещен И 9, разрешен И 8).

В режиме измерения степени стартстопных или степени синхронных искажений второй триггер 7 н состояние 0 может быть обращеи -олько сигналом с выхода блока сравнения 13.

При наличии нулевых искажений в блоке памяти 11 и блоке счета 10 вы636814 ходным сигналом блока сравнения 13 второй триггер 7 устанавливается в состояние 0 (фиг. 2,е), и содержимое блока счета 10, соответствующее величине первого измеряемого искажения, по сигналу, соотнетствующему положительному перепаду напряжения на выходе блока формирования идеальных значащих моментов восстановления 3, или по сигналу со второго выхода фазового дискриминатора 2 перезаписывается в блок памяти 11.

Эти же сигналы поступают на саот- )О ветствующие входы установки в 1 второго триггера 7, и если величина искажения следующей измеряемой посылки (фронта), отсчитывается в блоке счета 10 в момент перезаписи ее в блок памяти ll, по абсолютной величине меньше содержимого блока памяти 11, то перезапись происходит,так как элементы И 8 и 9 запрещены сигналом с выхода второго триггера 7. Если же величина этого искажения больше, та в момент, когда содержимые блока счета 10 и блока памяти 11 равны, блок сравнения 13 выдает сигнал (фиг.2,д), сбрасывающий второй триггер 7 в 0 .

Сигналы с выхода второго триггера (фиг.2,е) разрешают элементы И 8 и

9 и саотнетствующим сигналом перезаписи (в примере сигнал с выхода И 9 фиг.2,ж) содержимое блока памяти 11 заменяется большим по абсолютной вели-3( чине содержимым блока счета 10.

Время измерения степени искажения задается в блоке установки режимов 5 и поступает н блок памяти 11 как сь.-нал сброса в состояние 00...00 .,35

Предложенный измеритель краевых искажений дискретных сигналов поэналяет повысить точность измерения во всем диапазоне до точности в наименьшем диапазоне известнога устройства беэ 40 увеличения количества оборудования.

Кроме того, из устройства исключается громоздкий и сложный переключатель диапазонов, что упрощает технологию изготовления устройства и ега эксплуатацию.

Формула изобретения

Измеритель краевых искажений дискретных сигналов, содержащий последовательна соединенные блок согласования и фазовый дискриминатор, второй вход которого соединен с ега перным входом через блок формирования идеальных значащих маментон восстановления, второй вход которого соединен с выходом генератора, а также блок установки режимов и блок памяти, о т л ич а ю шийся тем, что, с целью повышения точности измерений, введены первый и второй триггеры, первый и второй элементы И, блок счета, дешифратор и блок сравнения, при этом выход блока формирования идеальных значащих моментов васстановлечия подключен к первому и второму входам первого триггера, к первому входу второго триггера, к первому входу первого элемента И и первому входу блока счета, нтараи вход которого соединен с третьим входом первого триггера и с первым выходом фазового дискриминатора, второй выход которого подключен к четвертому входу первого триггера, ка нтарому входу второго триггера и к первому входу второго элемента И, второй вход которого соединен са вторим входом первого элемента И и с выходом второго триггера, третий нхад которого соединен с первым выходом блока установки режимон, í "opoA, -ретий и четвертый выходы катарага подключены соответственна к третьему входу первого элемента

И, к третьему входу второго элемента

И и к первому .ВхОдУ блОк= и"MRTP BTo рай, третий и четвертый входы которого соединены соответственна с выходом второго элемента И, с выходам первого элемента И и с выходом блока счета, третий и четвертый входы которого соединены соответственно с выходом первого триггера и с выходом генератора,. выход блока памяти подключен ка входу дешифратора и к первому нходу блока сравнения, второй вход которого соединен с выходом блока сче — à, а выход блока сравнения подключен к четвертому входу второго триггера.

Источники информации, принятые на внимание при экспертизе:

i. Авторское свидетельство СССР

9 524325, кл. Н 04 L ll/08, 1974.

636814

Составитель Г. Челей

Техред К.Гаврон Корректор И. Гоксич, Редактор И. Карпас

Заказ 6971/5О Тираж 763 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4