Блок управления для запоминающего устройства

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (6l) Дополнительное к авт. свид-ву (22) Занвлено 06.01.75 (21) 2094258/18-24 с присоединением заявки М— (23) Приоритет (43) Опубликовано 15.12.78.Бюллетень № 46 (45) Дата опубликования описания 15.12.78 (51) М. Кл

Q 05 В 19/18

С ll С 19/00

1оаудвротвенный номнтет

Соввта Министров СССР во делам изобрвтеннй н открытий (53) УДК 621.327 (088.8) Р ГС )3:>- ч

В. И. Осипенко, А. Q. Хоменко, Г. П. Ляпов

В. В. Проценко и В. П. Чекалкии (72) Авторы изобретения

БИБЛИОТЕК,х (71) Занвитель (54) БЛОК УПРАВЛЕНИЯ ДЛЯ ЗАПОМИНАЮШЕГО

УСТРОЙСТВА

Изобретение относится к радиотехническим устройствам и может быть использовано для управления запоминающими устройствами и устройствами обработки информации.

Известно устройство обработки информации (I ), выполненное на логических элементах.

Недостатком этого устройства является то, что оно используется для обнаружения повторяющихся сигналов при одном. постоянном периоде слелования сигналов.

Наиболее близким по технической сущнос ти к предлагаемому изобретению является блок управления, содержащий регистр, первый вход которого подклк>чен к единичному входу основного триггера и к первой шине управления, второй вход регистра соединен с одним из входов первого элемента И и второй шиной управления, другой вход первого элемента И соединен с единичным выходом основного триггера, выход первого элемента И полках>чен к выхолу блока управления (2}. Время задержки (длина) регистра и регистров запоминакццего устройства определяется частотой следования управляющих сигналов

Известное устройство может осуществлять обработку информации только при одной определенной частоте управляющих сигналов, так как длина регистра управления не изменяется.

Однако в практике часто возникает необходимость накопления информации при двух и более частотах управлянццих сигналов.

Целью изобретения является расширение области применения блока управления для за поми на ю щего устройства.

Цель достигается тем, что в предлагаемый блок управления введены элемент ИЛИ, дополнительные триггеры и элементы И, один из входов второго и третьего элементов И соединены с первым выходом регистра, второй выход которого подключен к лругому входу второго и одному из входов четвертого элементов И, третий выхол регист2В ра соединен с одними из входов пятого и шестого элементов И, другие входы которых соединены с нулевым и единичным Bhlходами первого лопол нител ьнсл о три г гера

637786 соответственно, олин из входов которого соединен с выходом второго элемента И, другой вход — с первой шиной управления, выходы пятого и шестого элементов И соединены ссютветственно со входами второго дополнительного триггера, первый выход которого подключен к другому входу третьего элемента И, в арой выход второго дополнительного триггера соединен с другим входом четвертого элемента И, выходы третьего н четвертога элементов И подключены через элемент

ИЛИ к нулевому входу основного триггера.

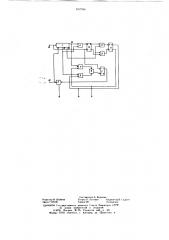

На чертеже приведена функциональная схема предлагаемого устройства, содержащего регистр l, основной триггер 2, элементы И 3 — 8, элемент ИЛИ 9, дополнительные триггеры 10, 11, шины управления 12, 13.

Устройство работает следующим образом.

Управляющие сигналы определяют момент времени начала процесса записи и сдвига информации в устройствах обработки информации (накопители, ЗУ и др.) и поступают по первой шине управления !3 на вход регистра 1 и единичные входы триггеров 2, 10. На вторую шину управления поступают импульсы сдвига информации в накапливающих линейках устройств обработки информации.

Б исходном состоянии триггер 2 запрещает прохождение через элемент 3 импульсов сдвига информации на устройство обработки информации. С приходом управляющего импульса триггер 2 устанавливается в единичное состояние, разрешая прохождение через элемент 3 импульсов сдвига на накапливающие линейки устройства обработки информации.

Одновременно, при поступлении управляющего импульса устанавливается в единич ное состояние триггер 10 и первый разряд регистра 1, и по импульсам сдвига, поступающим на второй вход регистра l происходит последовательная установка в единичное состояние последующих разрядов. Прелылущие разряды регистра l при этом возвращаются в нулевое состояние. На выходах 14, 15 регистра l вырабатываются импульсы, задержанные относительно управляющих.

Время задержки этих импульсов определяется количеством разрядов между входом и соответствующим выходом регистра 1 и частотой следования импульсов сдвига, поступакицих на регистр l, Количество разрядов регистра l межлу промежуточным 15 и основным 14 выходами регистра 1 выбирается так, чтобы время задержки сигнала на этом участке регистра равнялось периоду повторения управляющих импульсов, следующих с более высокой частотой. Дополнительный выход 16 регистра выбирается между промежуточным !5 и основным 14 выходами и является вспомогательным выходом !6, необходимым лля ра55 выходе элемента 4 вырабатываются импульсы, которые переводят триггер 10 опять в нулевое состояние, после чего нулевое состояние триггера 11 подтверждается импульсами, поступающими на его нулевой вход с дополнительного выхода !6 регистра !. !!ри низкой частоте следования управлякпних импульсов fg на выходе элемента 4 боты схемы автоматического опрелел ния частоты следования управляюпшх импульсов.

По истечении времени, равного периолу повторения управляющих импульсов, следующих с частотой fq, на выходах 14 и 15 регистра 1 вырабатываются импульсы, которые поступают на входы элемента 4, в результате чего на его выходе появляется сигнал, ко IO тарый переводит триггер 10 в нулевое состояние. Потенциал, который вырабатывается на нулевом выходе триггера 10, разрешает прохождение через элемент 5 на нулевой вход триггера 11 импульсов, поступающих на элементы 5 и 6 с дополнительного выхода !6 ! регистра 1. Через элемент 6 этот импульс не проходит, так как в это время он заблокирован запрещающим потенциалом, которь|й подается на схему с единичного выхода триггера 10. Триггер 11 переводится в нулевое состояние и íà era нулевом выходе

>О вырабатывается разрешающий потенциал, который поступает иа элемент 8 и на устройство обработки информации (или ЗУ), при этом в нем подключаются накапливающие линейки с временем задержки (длиной), соответствующим перйоду повторения управляющих импульсов следующих с частотой fi.

Устройство обработки информации при этом осуществляет накопление си гнал ов, поступающих на его вход с частотой, синхронной частоте управляющих импульсов fi. На вызО ходе вырабатывается сигнал обнаружения.

Через элемент 8 и элемент ИЛИ 9 на нулевой вход триггера 2 подается управляющий импульс, вырабатываемый на выходе 15 регистра 1. Этим импульсом триггер 2 воз35 вращается в исходное нулевое состояние и запрещает прохождение через элемент 3 импульсов сдвига на устройство обработки информации.

Следующий управляющий импульс, который поступает с шины 13 на вход регистра 1 и единичные входы триггеров 2 и 10, переводит триггер 2 в единичное состояние, при этом триггер 2 разрешает поступление импульсов сдвига информации через элемент 3 н а устройство обработки информ а ции. Таки м образом осуществляется следующий цикл накопления информации.

Разрешающий потенциал, который вырабатывается в этом случае на единичном выхоле триггера 10, при частоте следовния импульсов f не изменяет нулевого состояния триггера 11, так как после каждого управляюц его импульса, начиная со второго, на