Последовательное суммирующее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i i) 6378П

Сава Советова

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 05.03.74 (21) 2003769/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.12.78. Бюллетень № 46 (45) Дата опубликования описания 15.12.78 (51) М. Кл,2

G 06F 7/385

Государственный комитет

Совета Министров СССР по дедам иаобретеннй н открытий (53) УДК 681.325.5 (088.8) (72) Авторы изобретения Л. А. Ромашкина, А. И. Мартынюк, М. Г. Попова и А. В. Николаев (71) Заявитель (54) ПОСЛЕДОВАТЕЛЬНОЕ СУММИРУЮЩЕЕ

УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть применено при построении арифметических устройств последовательного типа.

Известны последовательные суммато- 5 ры (1, 2). Наиболее близким к изобретению является последовательное суммирующее устройство, содержащее одноразрядный сумматор, к первому и второму входам которого подключены входные шины операн- 10 дов устройства, и к выходу суммы одноразрядного сумматора подключена выходная шина устройства (3). Этот сумматор характеризуется зависимостью быстродействия от параметров, используемых для 15 хранения переносов элементов памяти; новый перенос не может быть передан на элемент задержки, если он еще не освободился от предыдущего. Кроме того, такие элементы задержки имеют низкую надежность, 20 что понижает надежность всего устройства в целом.

Целью изобретения является повышение быстродействия и увеличение надежности.

В описываемом устройстве это достигается 25 тем, что оно содержит два триггера, элементы И и ИЛИ, причем единичные входы триггеров подключены к выходу переноса одноразрядного сумматора, нулевые входы первого и второго триггеров подключены 30 соответственно к первой и второй тактовым шинам, а единичные выходы первого и второго триггеров — к первым входам соответственно первого и второго элементов И, вторые входы которых подключены соответственно ко второй и первой тактовой шинам, а выходы — ко входам элемента ИЛИ, выход которого соединен с третьим входом одноразрядного сумматора.

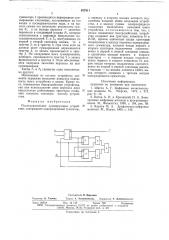

На чертеже представлена схема описываемого устройства.

В состав устройства входят одноразрядный сумматор 1, триггеры 2 и 3, элементы

И 4 и 5 и элементы ИЛИ 6.

К первому и второму входам одноразрядного сумматора 1 подключены входные шины операндов х и у. Выход суммы одноразрядного сумматора 1 подключен к выходной шине устройства, а выход переноса— к единичным входам триггеров 2 и 3, нулевые входы которых соединены с первой и второй тактовыми шинами. Первые входы элементов И 4 и 5 подключены к выходам соответственно триггеров 2 и 3, вторые входы соответственно — ко второй и первой тактовым шинам, а выходы ко вторым элементам ИЛИ 6, выход которого соединен с третьим входом одноразрядного сумматора 1.

При работе суммирующего устройства в

63781 1

Составитель В. Березкин

Техред Л. Камышникова Корректор Т. Добровольская

Редактор Л. Тюрина

Заказ 2637/4 Изд. М 142 Тираж 799 Подписное

НПО Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

3 сумматоре 1 производится поразрядное суммирование слагаемых, поступающих на его входы в последовательном коде, и на выходе суммы его возникают результаты суммы S;, а на выходе переноса — значение переносов в следующий разряд Р;, которые записываются с помощью импульсных последовательностей Т1 и Т>, поступающих по первой и второй тактовым шинам, то в триггер 2, то в триггер 3. При этом если на данном шаге суммирования опрашивается триггер 2, то запись производится в триггер 3. На следующем шаге суммирования, наоборот, опрашивается триггер 3 и запись производится в триггер 2. Этим обеспечивается задержка значения переноса на шаг суммирования.

Такты Т1 и Т2 сдвинуты один относительно другого.

Исключение из состава устройства элемента задержки позволяет повысить надежность всего устройства в целом. Кроме того, повышается быстродействие устройства, так как использование цепи переноса двух параллельно работающих триггеров позволяет повысить тактовую частоту устройства.

Формула изобретения

Последовательное суммирующее устройство, содержащее одноразрядный сумматор, к первому и второму входам которого подключены входные шины операндов устройства, а к выходу суммы одноразрядного сумматора подключена выходная шина устройства, отличающееся тем, что, с целью повышения быстродействия, устройство содержит два триггера, элементы И и

ИЛИ, причем единичные входы триггеров подключены к выходу переноса одноразрядного сумматора, нулевые входы первого и второго триггеров подключены соответственно к первой и второй тактовым шинам, а единичные выходы первого и второго триггеров — к первым входам соответственно первого и второго элементов И, вторые входы которых подключены соответственно ко второй и первой тактовым шинам, а выходы — ко входам элемента ИЛИ, выход которого соединен с третьим входом одноразрядного сумматора.

Источники информации, принятые во внимание при экспертизе

1. Шигин А. Г. Цифровые вычислительные машины. М., Энергия, 1971, с. 212, рис. 9 — 19.

2. Китов А. И. и Криницкий Н. А. Электронные цифровые машины и программирование. М., Физматгиз, 1959, с. 164, рис. 59.

3. Карцев М. А. Арифметико-цифровые машины. М., Наука, 1969, с. 143.