Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Респубпик (6!) Дополнительное к авт. свид-ву (22) Заявлено 01.0876(2!) 2392195/18-24 с присоединением заявки №(23) Приоритет— (43) Опубликовано 15.12.78.Бюллетень № 46 (45) Дата опубликования описания ) 51278 (5!) М, Кл, Cj06 Г 11/04

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (оа) УДК 681. 326. . 7 (088. 8) (72) Авторы изобретения

В. Н. Купенко, Е. Е. Емнов, Н. Т. Березюк, Н. и К. К.фурманов (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ

Изобретение относится к области вычислительной техники и может быть использовано для программного контроля схем цифровых приборов, больших интегральных схем в условиях серийного производства.

Известно устройство для контроля логических блоков, содержащее запоминающее устройство для хранения тестов, регистр теста, устройство записи информации из запоминающего устройства в регистр теста, формирователи выходных и входных сигналов, коммутационное устройство и устройство сравнения (11 .

Недостатком такого устройства является низкое быстродействие.

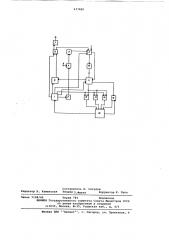

Наиболее близким по технической сущности к данному изобретению, является устройство для контроля логических блоков, содержащее блок памяти, блок управления, генератор стимулирующих воздействий, коммутатор, блок сравнения, блок памяти неисправностей, блок формирования сигнала ошибки, ре25 гистр подпрограмм, регистр сбоев, регистр цикла, регистр возврата, адресный коммутатор, причем первый, второй, третий, четвертый и пятый выходы блока памяти соединены соответственно с первым входом генератора стимулирующих воздействий, с первым входом блэка управления, с первым входом блока сравнения, с первыми входами регистра подпрограмм, регистра сбоев и регистра цикла, с первым входом блока формирования сигнала ошибки, первый, второй и третий выходы которого соединены соответственно со вторым входом блока управления, с первым входом регистра возврата, со вторыми входами регистра подпрограмм, регистра сбоев, регистра цикла, выходы регистра подпрограмм, регистра сбоев, регистра цикла, регистра возврата соединены соответственно с первым, вторым, третьим и четвертым входом адресного коммутатора, первый и второй выходы которого соединены соответственно co аходом блока памяти и со вторым входом блока возврата, выход блока управления соединен со вторым входом генератора стимулирующих воздействий, первый и второй выходы которого соединены соответственно со входом коммутатора и со,вторым входом блока сравнения, выход коммутатора является выходом устройства, вход устройства соединен с третьим входом блока сравнения, первый и второй выходы которого соеди637820

При несоответствии накопленной и эталонной информации блок формирования сигнала ошибки 11 вырабатывает команду обращения к подпрограмме локализации неисправности через регистр сбоя 13. Адрес подпрограммы записывается блоком памяти 1 в регистр подпрограмм 12.

Блок памяти l в этом случае через генератор стимулирующих воздействий

6 и коммутатор 7 выдает на объект проверки кодовые комбинации.

Все случаи несоответствия реакций 10 объекта проверки с эталоном фиксируются блоком памяти неисправностей 10.

По окончании подпрограммы блок выработки сигнала ошибки 11 определяет вид неисправности и переходит к сле- )5 дуняцему участку программы по адресу, записанному ранее в регистре возврата 15 с адресного коммутатора 16 в момент перехода к подпрограмме локализации неисправности. 20

По окончании всей программы контроля и отсутствии неисправностей объект проверки считается исправным.

3а счет введения регистра масок, блока хранения масок, блока формирования масок возрастает быстродействие устройства, так как уменьшается количество .анализируемых кодовых комбинаций.

Формула изобретения

Устройство для контроля логических блоков, содержащее блок памяти, блок управления, генератор стимулирующих воздействий, коммутатор, блок сравнения, блок памяти неисправностей, блок формирования сигнала ошибки, регистр подпрограмм, регистр сбоев, регистр цикла, регистр возврата, адресный коммутатор, причем первый, второй, третий, четвертый и пятый выходы блока памяти соединены соответственно с первым входом генератора стимулирующих воз- 40 действий, с первым входом блока управления, с первым входом блока сравнения, с первыми входами регистра подпрограмм, регистра сбоев и регистра цикла, с первым входом блока формирования сигнала ошибки, первый, второй и третий выходы которого соединены соответственно со вторым входом блока управления, с первым входом регистра возврата, со вторыми входами регистра подпрограмм, регистра сбоев и регистра цикла, выходы регистра подпрограмм, регистра сбоев, регистра цикла, регистра возврата соединены соответственно с первым, вторым, третьим и четвертым входом адресного коммутатора, первый и второй выходы которого соединены соответственно со входом блока памяти и со вторым входом блока возврата, выход блока управления соединен со вторым входом генератора стимулирующих воздействий, первый и второй выходы которого соединены соответственно со входом коммутатора и со вторым входом блока сравнения, выход коммутатора является выходом устройства, вход устройства соединен с третьим входом блока сравнения, первый и второй .выходы которого соединены со входом блока памяти неисправностей, со вторым входом блока формирования сигнала ошибки, выход блока памяти неисправностей соединен с третьим входом блока формирования сигнала ошибки, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия, в устройство введены регистр масок, блок хранения масок, блок формирования масок, причем шестой выход блока памяти соединен со входом регистра масок, выход которого соединен с первым входом блока хранения масок, второй вход блока хранения масок является вторым входом устройства, выход блока хранения масок соединен со входом блока формирования масок, выход которого соединен с четвертым входом блока сравнения.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

Р 390526, кл. $06 F 11/04, 1971.

2. Авторское свидетельство СССР

У 469971, кл. G 06 F 11/00, 1973.

Составитель И. Сигалов

Редактор Н. Каменская .Техред З.фанта Корректор Е, Папп

Заказ 7 108/40 Тираж 784 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4