Интегральная ячейка памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республин

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВМДВТИЛЬСТВУ (61) Дополнительное к авт. свил-ву ¹ 534792 (22) Заявлено 25.01.77 (21}2445569у18 24 с присоединением заявки №(23) Приоритет(43) Опубликовано 15.12.78.Бюллетень № 46 (45) Дата опубликования описания 20,12.78

637867 и (51) М. Кл.

5 11 С 11/40

Государственный коинтет

Совета Инннотроа СССР оо делам нзобретеннй н откритнй (53) УДК 681.327..67 (088.8) (72) А,втор изобретения

С. М. Кононов (71) Заявитель (54) ИНТЕГРАЛЬНАЯ ЯЧЕЙКА ПАМЯТИ

Изобретение относится к вычислительной технике и предназначено для использования в качестве элемента памяти интегральных запоминающих устройств с полностью инжекционным. пиганием.

Известна ячейка памяти, защищенная основным -авт. св. N 534792, содержащая транзистор, коллектор которого соединен с базой И Р тт — транзистора, первый эмиттер которого соединен с пер- 10 вой адресной шиной, второй - с шиной считывания, коллектор - с базой P-hPтранзистора, первый эмиттер которого соединен с второй адресной шиной, дополнительный П " p тт " тр анзисгор, база кото- 15 рого соединена с вторым эмигтером р тт < р транзистора, коллектор — с базой рдтт» р-т транзистора и эмиттер - с шиной записи. Известная ячейка характеризуется невозможнбстью согласования с об- о служивающей электроникой с полностью инжекционным питанием; необходимостью создания сттециальнь1х формирователей аа2 ресных сигналов; высокой потребляемой

\ мощностью

Описываемая ячейка памяти является развитием известной, защищенной основным авг.св. N 534792, и отличается от нее тем, что в ней Il — p — тт — транзистор и дополнительный тт-p-tl — транэиотор выполнены с дополнительными эмиггерами, соединенными с соответствующими базами, а база дополнительного тт-Р-„Фетранзистора соединена с первым эмигтеромИ- р-тт.- транзистора. Это позволяет снизить потребляемую мощность и повысить быстродействие.

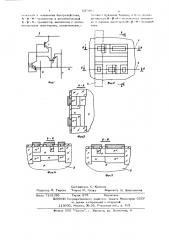

На фиг. 1 показана принципиальная электрическая схема описываемой ячейки; на фиг. 2 - ячейка в интегральном исполнении, вид сверху; на фиг. 3 - то же, сечение по А-А на фиг. 2; на фиг. 4то же, сечение по Б-Б на фиг. 2; на фиг.

5 - го же, сечение по В-В на фиг; 2.

Пер вый коллектор двухколлекторного

Р, транзистора 1 соединен с базой

637867 и первым эмиттером трехэмиттерного

И вЂ” P 0 — транзистора 2. Второй коллектор транзистора 1 подключен к базе двухэмиттерного fl-p- o- транзистора 3 и к шине 4 выбора слова, к которой присоединены также второй эмиттер транзистора 2 и первый эмиттер транзистора 3.

Эмиттер транзистора 1 связан с шиной 5

1 питания. Третий эмиттер транзистора 2 присоединен к первой шине 6 считывания- 1ц записи. Второй эмиттер транзистора 3 подсоединен к шине 7 считывания — записи.

Соединение эмиттеров транзисторов 2 и 3 с их базами необходимо дпя уменьшения накопления носителей при переходе этих транзисторов в включенное состояни е. Тр анзистор 3 должен иметь прямой и инверсный коэффициенты усиления по току больше единицы.

Интегральная ячейка памяти работает в трех режимах: записи, считывания и хранения.

И процессе работы ячейки памяти на шине 5 установлен постоянный уровень потенциала порядка (0,7 — 0,8) В, а высокие или низкие уровни потенциалов на шинах 4,6 и 7 совместимы с уровнем потенциалов в устройствах с полностью инжекционным питанием.

В режиме записи логической "1" на шину 4 подается сигнал выбора слова (высокий уровень потенциала), а на шинах 6 и 7 создается режим холостого хода. В результате транзисторы 1, 2 и 3 выклю чаются. Если после этого, не изменяя уровня потенциалов на шинах 6 и 7, на шину 4 подается низкий уровень потенциала, то запоминающий элемент, образованный транзисторами 1 и 2, остается в со стоянии хранения логической "1", и процесс записи логической "1" заканчивается.

3 режиме записи логического "0", пос» ле подачи на шину 4 сигнала выбора слова, на шины 6 и 7 подаются низкие уров- ни потенциалов, в результате транзистор

3 включается и создает на базе транзистора 1 низкий уровень потенциала, после чего последний выключается, и ток одного из его коллекторов течет в базу транзис- о тора 2, который также переходит в включенное состояние. Поэтому, после подачи на шину 4 низкого уровня потенциала, не изменяя уровней потенциалов на шинах 6 и 7, запоминающий элемент на транзисто55 рах 1 и 2 устанавливается в режим хранения логического "0, и процесс записи логического "0" заканчивается, В режиме считывания перец подачей сигнала выбора слова на шину 6 необходимо подавать низкий уровень потенциала, а на шине 7 — создавать режим холостого хода. Тогда, после подачи»а шину 4 сигнала выбора слова, транзистор 3 выключается в инверсном направлении, если запоминающий элемент на транзисторах 1 и

2 находится в состоянии хранения логического "0,,или остается выключенным, если запоминающий элемент находится в состоянии хранения логической 1". В пепвом случае на шине 7 устанавливается низкий уровень потенциала, а во втором случае сохраняется высокий уровень потенциала, соответствующий режиму холостого хода. Изменение уровня потенциала на шине 7 относительно уровня потенциала на шине 6 регистрируется усилителем считывания (на чертеже не показан).

В режиме хранения ячейка памяти p&ботает, если перед подачей сигнала выбора слова на шину 4 на шине 7 создается режим холостого хода, а на шину 6 подается низкий уровень потенциала.

Соединение второго коллектора р- t1 -ртранзистора 1. с шиной 4 выбора слова исключает создание мощного генератора тока в формирователе сигнала выбора слова. В последнем случае генератор тока должен обеспечивать ток, необходимый для включения только одного транзистора считывания — записи во всем слове, и то при условии, что запоминающие элементы всех ячеек памяти данного слова находятся в состоянии хранения логической "1 .

Во всех остальных случаях, когда определенная часть запоминающих элементов в слове находится в состоянии хранения логического 0", базовые токи транзисторов считывания -записи в соответствующих ячейках памяти обеспечиваются коллекторами Р- П-Р- транзисторов.

Конструктивные особенности описываемой интегральной ячейки памяти обеспечивают непосредственное согласование с обслуживающей электроникой с полностью инжекционным питанием, низкую потребляемую мощность, а также более высокое ее быстродействие.

Формула изобретения

Интегральная ячейка памяти по авт. св, М 534792, отличающаяся тем, что, с целью снижения потребляемой

6378,3 i тора.

Г Ума.t

А-A Л д

ФиаЯ

8-8

Составитель С. Кононов

Редактор Л. Тюрина Техред М. Петко Корректор Н. Золотовская

Заказ 7161/50 Тираж 675 Подписное

0НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 м .тцности и повьппения быстродействия, и — P — 8 — транзистор и дополнительный

И вЂ” p — И вЂ” транзистор выполнены с дополнительными эмиттерами, соединенными с: соотвегсгвуюи ими базами, а бп та донолнигель ого n — P — n — тр:нзпс рп соеди

HB c l10f1Bb7M эмпт тером fl — P — F1 — транзид