Преобразователь декартовых координат

Иллюстрации

Показать всеРеферат

ОП И

ИЗОБРЕТЕНИЯ

Сеюз Соаетсннк

Соцналнстнчесинк

Республик оц6389УУ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) ЗайвлЕно 290376 (2т) 2341176/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.1 278. Бюллетень № 47 (45) Дата опубликования описания 281278 (Sl) М. Кл.

606 g 7/22

Государственный комитет

Совета Министров СССР но делам изобретений и открытий (53) УДК 681. 335 (088. 8) (72) Авторы

ИЗОбрЕтЕНИя А. Б. Артамонов, А. Н. Жариков и А. M. Смирнов (71) Заявитель

Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) (54) ПРЕОБРАЗОВАТЕЛЬ ДЕКАРТОВЫХ КООРДИНАТ

Изобретение относится к области вычислительной техники и предназначено для реализации зависимостей, описывающих поворот плоской декартовой системы координат:

Х = Х. Со&<А. У 5тпс(.

-"-Х &1пА + У cosd. ((1

Известны преобразователи декартовых координат, в которых реализуется поворот на заданный угол, а входные и выходные величины представлены напряжениями постоянного тока.

Одно из известных устройств,реализующих поворот системы координат, построено на синусно-косинусных вращающихся трансформаторах (1 . Однако это устройство имеет ограниченное быстродействие электромеханической системы отработки заданного угла поворота.

Наиболее близким к изобретению по технической сущности является электронный преобразователь декартовых координат, содержащий первый интегратор, вход которого через первый управляющий ключ соединен с первым входом пре-образователя, а выход — с первым входом компаратора, второй вход которого связан с вторым входом преобразовате,ля, второй интегратор, выход которого через второй управляемый ключ соединен с входом третьего интегратора, инвертор, выход которого через третий управляемый ключ подключен к входу второго интегратора, шины начальной установки второго и третьего интеграторов соединены через четвертый и пятый управляемые ключи соответственно с третьим и четвертым входами преобразователя, а шина начальной установки первого интегратора через шестой управляемый ключ соединена с нулевой шиной (2) .

Недостатком данного преобразователя является невысокое быстродействие.

Цель изобретения — повышение быстродействия.

Это достигается тем, что в преобразователь дополнительно введены двухканальный аналоговый запоминающий блок, двухразрядный дискретный делитель напряжения, подключенный входом к первому входу преобразователя, а выходом — ко второму входу компаратора, блок управления, подключенный к выходу компаратора, вход двухканального аналогового запоминающего блока через дополнительно введенные седьмой и восьмой управляемые ключи связан соответственно с входом и выходом ин638977 формула изобретения когда или вертора, вход инвертора через дополнительно введенные девятый и десятый управляемые ключи связан соответственно с выходами второго и третьего интеграторов, управляющие входы ключей, двухразрядного дискретного делителя .напряжения и двухканального аналогового запоминающего блока связаны с 5 соответствующими выходами блока управления, а между вторым входом преобразователя и вторым входом компаратора включен масштабирующий резистор.

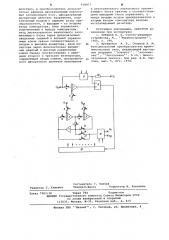

На чертеже дана структурная схема ð предложенного устройства.

Преобразователь содержит интеграторы 1, 2 и 3, управляемые ключи 4, 5 и

6, инвертор 7, компаратор 8, двухразрядный дискретный делитель 9 напряжения,масштабирующий резистор 10, управляемые ключи 11-17, двухканальный аналоговый запоминающий блок 18, блок 19 управления.

Преобразователь работает следующим образом.

Цикл работы состоит из пяти тактов. Первый. такт прецназначен для установки начальных условий интеграторов 1, 2 и 3, для чего замыкаются ключи 4, 5 и б. Во втором такте с по мощью убывающего двоичного кода, вырабатываемого в блоке 19 управления и поступающего на делитель 9, в результате сравнения его с напряжением (), определяется номер квадранта угла поворота координат. При срабатывании компаратора 8 номер квадранта, моделируемый отношением напряжений — фиксируется в блоке 19 управлеЙи я

Б третьем так е замыкаются ключи

11, 12, 14 и 15. В результате в замкнутом контуре, образованном интегратораМи 2 и 3 и инвертором 7,вырабатываются гармоничные напряжения, определяемые начальными .условиями U), и U и временем интегрирования.

Интегратор в это время вырабатывает линейно нарастающее напряжение

О

02

И4 т„У 45 где Т вЂ” постоянная времени интегратора 1.

Это напряжение сравнивается в компараторе 8 с напряжением

4 Г и .г 50 где П вЂ” номер квадранта входного агрумента.

В момент срабатывания компаратора, т,/u„„ (у 4 / ключи 11р 12, 2

14 и 15 размыкаются и интеграторы 2 и 3 запоминают накопленные в них значения: 65

Uä U Со5 — —" — — +U &1ц 1 (z) где Т вЂ” постоянная времени интегра2 тора 2 и 3, Прй +-.д.(аргумент гармонических функций в соотношениях (1) и (2) представляется в виде {ы,> + и +-), где

С(-,1 меняется в пределах от 0 до 90

В четвертом и пятом такте работы сигналы с интеграторов 2 и 3 последовательно переписываются в ячейки запоминающего блока 18.

Для первого квадранта (П = О) в первую ячейку запоминающего блока 18 сигнал подается через ключи 13 и 16 с выхода интегратора 2, а во вторую— с выхода интегратора 3 через ключи 15 и 16.

Для второго квадрачта (П = 1) в ячейку Х напряжение записывается с выхода интегратора 3 (через ключи !5 и

1b), а в ячейку У вЂ” с выхода ичтегратора 2 через ключ 13 7 и ключ 17.

Для третьего квадранта ячейка Х <

:связана с выходом интегратора 2 через

:ключи 13 и 1, а ячейка У вЂ” c выходом интегратора 3 через ключи 15 и 17.

Наконец, для четвертого квадранта в первую ячейку Х подается инверти( рованное напряжение интегратора 3 (замкнуты ключи 15 и 17), а во вторую ячейку Ч„ выходное напряжение интегратора 2 (замкнуты ключи 13 и 16).

Сокращение времени решения обусловлено,таким образом, сокращением времени интегрирования до четверти периода гармонического напряжения против полного периода в прототипе.

Преобразователь декартовых координат, содержащий первый интегратор, вход которого через первый управляемый ключ соединен с первым входом преобразователя, а выход — c первым входом компаратора, второй вход которого связан с вторым входом преобразователя, второй интегратор, выход которого через второй управляемый ключ соединен с входом третьего интегратора, инвертор, выход которого через третий управляемый ключ подключен к входу второго интегратора, шины начальной установки второго и третьего интеграторов соединены через четвертый и пятый управляемые ключи соответственно с третьим и четвертым входами преобраэОвателя, а шина начальной установки первого интегратора через шестой управляемый ключ соединена с нулевой шиной, отличающийся тем, что, с целью повышения быстро638977

Состанитель Г. Осипон

ТехредЭ.Фанта . Корректор H. Ковалева

Редактор T. Клюкина

Заказ 7283/38 Тираж 784 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 дейстния, в преобразователь дополнительно введены днухканальный аналоговый запоминающий блок, двухразрядный дискретный делитель напряжения, подключенный входом к первому входу преобразователя, а выходом — ко второму входу компаратора, блок управления, подключенный к выходу компаратора, 5 вход двухканального аналогового запоминающего блока через дополнительно введенные седьмой и восьмой управляемые ключи связан соответственно с входом и выходом инвертора, вход ин- 10 нертора через дополнительно введенные девятый и десятый управляемые ключи связан соответственно с выходами нторого и третьего интегратора, управляющие входы ключей, днухразрядного дискретного делителя напряжения и двухканального аналогового запоминающего блока связаны с соответствующими выходами блока управления, а между вторым входом преобразователя и вторым входом компаратора включен масштабирующий резистор.

Источники информации, принятые во внимание при экспертизе:

1. Лебедев А. П. Счетно-решающие устройства, М., Машиностроение, 1966, с. 194, 2. Артамонов А. Б., Смирнов A. М. функционат ьный преобразователь времяимпульсного типа, реализующий векторные операции поворот, разложение, построение . В сб.: Вычислительная техника. Под ред. В,Б. Смолона, нып. 5, ЛГУ, 1974.