Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТИЛЬСТВУ

Союз Советских

Социаписткческмх

Республик (и 639016 (61}Дополнительное к авт. свил-ау М.. 526019 (22) Заявлено 22.12.75(21) 2302252/18-24 (з13 М. Кл. с присоедииеииеее заявки №

6 11 С 11/00

Гиудврвтееннв1й квинтет

6еветв Инннетрев СИР ее делам нзобретеннй н атнрвэтнй (23) Приоритет— (43} Опубликовано 25.12.78рюллетень № 47 (53) УЛК 681. .827 (088.8) (45) Qara опубликования описания 27.12.78 } (72) Авторы изобретения

B. С. Голоборшенкэ, В. К. Броховец, П. И. Луговцов, В. Г. Рэманькэв и В. fl. Трофимов (71) Заявитель (54) ЗАПОМИ3}Л ОЩЕ}э УСТРОЙСТВ0 т5

Изобретение относится к запэминаюшим уст р ойств ам.

Известно устройство, содержашее регистр и дешифратор адреса, подключенные к накопителю, синхронизатор, регистр чис:!е, соединенный с выходным коммутатором. 5 э}одэстаткэм устройства является низкая эффективность его использования при работе с устройствами — потрабителямн, информационная разрядность которых меньше разрядности запоминаюшего устройства.

Из основного авт.св. % 52601 9 известно запоминакшее устройство, содержашее регистр адреса, выходы которого через дешифратор адреса подключены к адресным шинам накопителя, а его выходные шины через усилители воспроизведения подсоединены к одним из входов регистра числа.

При этом выходы регистра числа соедине» ны с одними из входов выходного коммутатора и через разрядные формирователи

20 с разрядными шинами накопителя, адресные шины — co входами регистра адреса, выходные шины устройства — с выходами выходного коммутатора, а входные шины устройства - c первыми входами входного коммутатора, выходы которого подключены ко вторым входам регистра числа. Устрэйст во также содержит блок управления, пер вый вход кэтэрэгэ соединен с первым вьехэдом синеээниз вторн ьтэ}эьэе ВхОди с выхэдами дешифратора вь:бора операции

Qo 1с-па у;э ;! E -:! D}сэгэ пэ,дючены " вц» ходам эегпс ра вьэбэра операци обмена, первые выходы блэка управления соединены с другими входами выходного коммутатора, вторые выходы — с третьими входами регистра числа, третьи выходы» со вторыми входами входного коммутатора и четвертыэ выходы - co вторыми входами усилителей воспроизведения.

При монопольном обращении к последовательно расположенным ячейкам памяти этогэ запэминаюшегэ устройства необходимо прп каждом обрашении формировать следуюший код адреса и код выбора операции обмена, передача которых снижает надежность системы в целом. Поэтому

63901 6 для органиэации монопольного режима используется счетный регистр адреса, в который заносится начальный код адреса и при каждом последующем обращении синхронизатор вырабатывает импульс, поступа- 5 ющий на счетный ахоп регистра адреса для выполнения команды по следующему адрОсу запоминающего устройства без передачи кода адреса по адресным шинам.

Недостатком известного устройстве яв- <0 ляется то, что монопольный режим возможен лишь при обмене с потребителем, данным с максимальной разрядностью (например, только славами) запоминающего устройства. Зто снижает надежность уст 15 ройства, так как при обмене денными укороченным форматом (например, при обмене полусловами и чвтвертьсловамибайтами)„ когда в зависимости от операции обмена нужно записывать в одну ячей-о ку запоминающего устройства, например полуслова или байты, такой режим невозможен, Цель изобретения - повышение надежности устройства. 1Я

Зто достигается тем, что устройство содержит дополнительный коммутатор, входы которого подключены соэтветственнэ к дополнительному выходу синхронизатора и выходам дешифратора выбора операции обмен" и регистра выбора операции обмена, а выходы дополнительного коммутатора соединены соответственно со входами регистра выбора операции обмена и со счетным вхэдом регистра адреса.

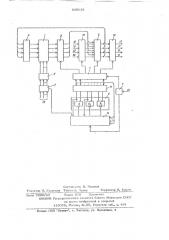

На чертеже дана структурная схема устройства, информационная разрядность которогo составляет, например, четыре байта.

Запоминающее устройство содержит на- О капитель 1, регистр 2 числа, усилители

3 воспроизведения, разрядные формирователи 4, регистр 5 адреса,,дешифратор 6 адреса, синхронизатор 7, регистр 8 выбора операции обмена, состоящий, например;. 5 из триггеров 9, дешифратор 10 выбора операции обмена, блок 11 управления, входной коммутатор 12, выходной коммутатор 13, дополнительный коммутатор

14, шины 15 24 причем 15, 17, 19 и

21 — выходные шины, 16, 18, 20 и 22входные шины, 23 - адресные шины, 24 — шина признак монопольного режима . Выходы регистра 5 адреса через деМ

55 шифратор 6 подсоединены к адресным шинам накопителя 1. Выходы накопителя 1 через усилители воспроизведения 3 подключены к первым входам регистра,н ла 2. Выходы регистра числа 2 соединены с одними иэ входов выходного коммутатора 13 и через разрядныв формирователи 4 соединены с разрядными шинами накопителя 1. Выходы входного коммутатора 12 подключены ко Вторым входаи рюгистра числа 2. Первый вход блока 11 управления соединен с первым выходом синхронизатора 7, вторые входы блока 11,с выходами дешифратора 10 выбора операции обмена, входы которого подключены к выходам регистра 8 выбэра операции обмена. Первые выходы блока 11 управления соединены с другими входами выходного коммутатора 13, вторые выходыс третьими входами регистра числа 2, третьи выходы — co вторыми входами входного коммутатора 12 и четвертые выходы блока 11 — со вторыми входами усилителей 3 воспроизведения, К первому входу коммутатора 14 подключен дополнительный выход синхронизатора 7. Ко вторым входам коммутатора 14 подключены выходы дешифратора 10 выбора операции обмена, к третьим входам - выходы регистра 8.

Выходы коммутатора 14 подключены K входам регистра 8 и счетному входу регистра адреса 5.

Устройство работает следующим образом.

Содержимое регистра 8 выбора операции обмена несет информацию о номерах шнн, по которым ведется обмен словами с потребителем; при обмене по одному байту - по шинам 15, 16, при обмене пэ полуслову — по шинам 15-18, при обмене по слову — пэ шинам 15-22.

Перед записью данных производится стирание следующим образом: во время операции стирания синхронизатор 7 выдает сигнал стробярования в блок 11 управления, который, анализируя результаты, выданные дешифратэром 10 выбора операции обмена, производит стрэбирование толь-. ко твх байтов данных, которые необходимо сохранять, а остальные байты в ре-гистр числа 2 не заносятся. При обмене данными с максимальным количеством байтов прочзводится стирание во всех байтах данных. Во время записи информация о данных, подаваемая по шинам 16,,8 илн

16 18 20 и 22 поступает на входной коммутатор 12. Синхронизатор 7 выдает сигнал приема данных в блок 11 управления, который анализирует состояние выхдов дешифратора 10 выбора операции обмена и с помощью входного коммутатора

12 производит перевод байтов с шин, на

639016 б ному байту блок 14 адресного управления осуществляет коммутацию импульса единичного приращения на счетный вход триггера 9 предыдушего разряда и коммутацию прямого выхода этого триггера 9 на счетный вход триггера 9 старшего разряда, а прямого выхода последнего - на счетный вход регистра 5 адреса, Благодаря такому подключению коммутатора 14 прежде, чем произвести запись новой информации в следующую ячейку накопителя

1 (при обмене по полуслову или о одному байту), производится распаковка полуслов (байтов)внутри ячейки, а затем переход к следующей ячейке накопителя 1.

В режимах чтения и чтения с записью новой информации взаимодействие всех блоков при обмене информацией по полуслову и байтам остается таким же, как и в режиме записи с монопольным признаком

Таким образом, предложенное запоминающее устройство позволяет производить последовательный прием-выдачу информации с учетом операции обмена и беэ пересылки кода адреса в запоминающее устройство от потребителя, что повышает надежность и расширяет функциональные возможности устройства которые они поступают (16 или 16 и

18), в те байты регистра 2, где информация должна быть записана и заранее произведено стирание прежней информации.

Затем обновленное содержимое всего регистра 2 числа через разрядные формирователи 4 записывается в накопитель 1.

Ф

При обмене данными с максимальным количеством байтов производится прием всех байтов данных по шинам 16, 18, 20 и 22. 10

В случае необходимости записи данных в последовательные ячейки накопителя 1 вместе с начальным кодом адреса, с которого нужно проводить запись и который 15 подается на адресные шины 23, на синхронизатор 7 подается признак монопольноrO режима по шине 24 и поддерживается до тех пор, пока осуществляется последоsaTem íaÿ запись. Поэтому, при наличии 20 признака монопольного режима, по второму обращению к запоминающему устройству на запись код адреса на адресные шины 23 не поступает, а импульс единичного приращения с синхронизатора 7 через 25 коммутатор 14 поступает на счетный вход регчстра адреса 5 и, тем самым, подготавливает чедуюпую ячейку накопитеря

1 для записи следующих данных Такое взаимодействие блоков запоминающего устройства справедливо при записи данчьж с максимальным количеством байтов (в нашем пример — «o слову). 1".ри обмене по полуслову с признаком монопольного режима сигналы с выходов дешифратора

10 выбора операции обмена осуществляют коммутацию импульса единичного прирыцения, ноступающего с синхронизатора 7 в коммутатор 14, на счетный вход триггера

9 старшего разряда (левый на ертеже) о регистра 8 выбора операции обмана. Прямой выход этого триггера 9 через коммутатор 14 соединяется сосчетным входом регистра адреса 5. При обмене по одФормула изобретения

Запомина1ощее устройство по авт.св.

%526019, oтличающееся тем, что, с ц ью гоеышения надежности устрэйc ва оно содержит дополнительный коммутатор, Hx 34 KoTopoI o lIonKJIio ieHbl соответственно и доголнительному выходу синхронизатора и выходам дешифратора выбора операции обмена и регистра выбора операции обмена, а выходы дополнительного коммутатора соединены соответственно со входами регистра выбора операции обмена и со счетным входом регистра anMOCRBll Гель В Р Д8Коа

ТBxti ., 9, 1у и Корректор И. Гокоич

l онактор !4 Ра=j мозй

Фцлиал ППП "Патент", г. Уигоуод, ул. Проектная, 4

Ддд яо gP gQ/Fj Q, ) ар ау;. Q (Q j +g+$)gljpно л

Й-1ИИ1Ы 1 ооуларотаенного но1 ;нтет, Сонета Мнннотроа (".:С(:.l ло лелаь1 нздор&теиий и Открыткй . Э 5 у, . у. З р „.< б, с5